Clock control block, I/o buffer, Internal oscillator – Altera MAX 10 Power User Manual

Page 15: Clock control block -2, I/o buffer -2, Internal oscillator -2

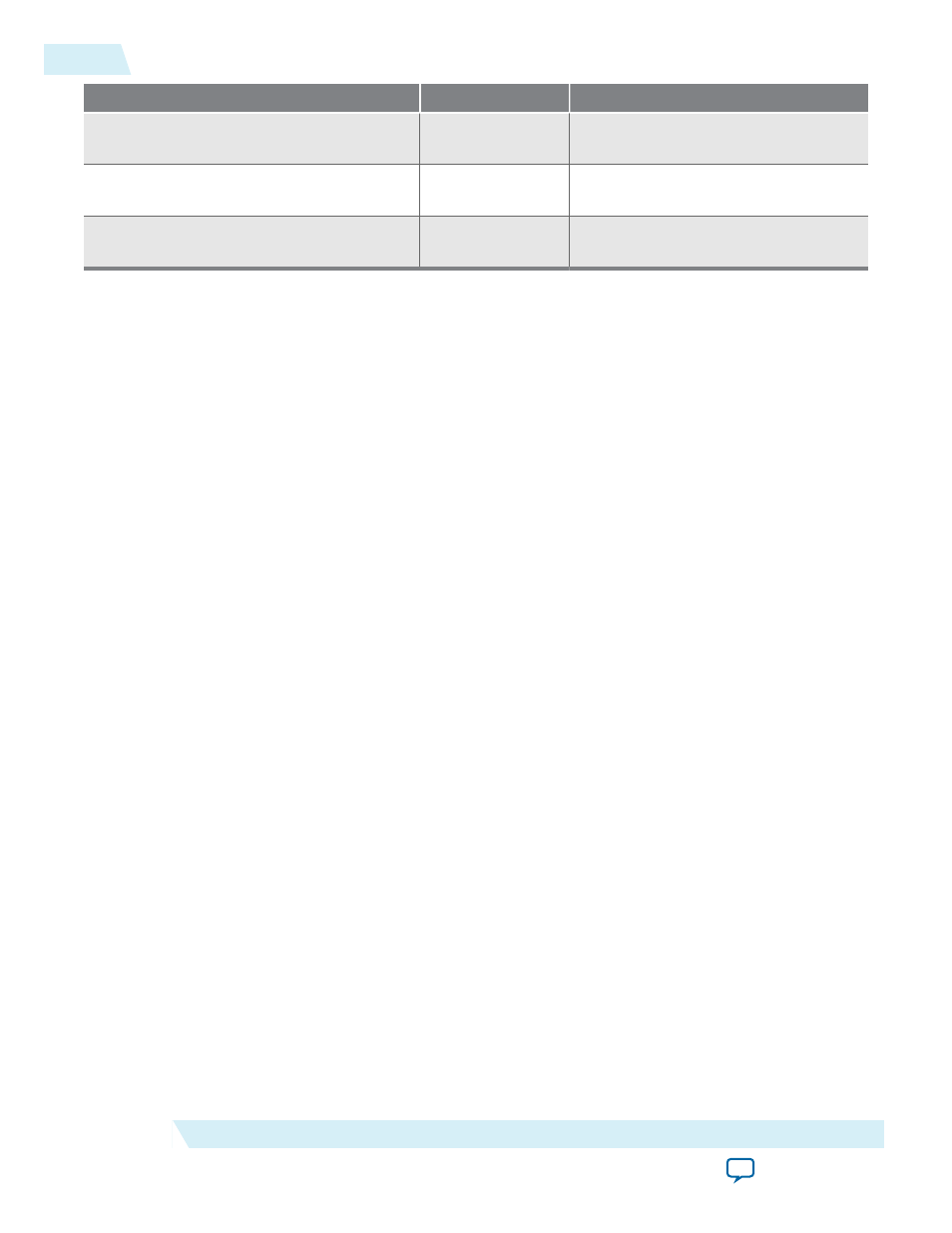

Port Name

Input/Output

Description

cnt_value[7:0]

Output

Free-running counter value in user

logic.

cnt_enter_sleep[7:0]

Output

Counter value when the system is

entering sleep mode condition.

cnt_exit_sleep[7:0]

Output

Counter value when the system is

exiting sleep mode condition.

The power management controller design is a FSM showing the state of powering down and powering up

global clocks (GCLKs) and I/O buffers. The internal oscillator, clock control block, and I/O buffer are

intellectual property (IP) that are supported by the Quartus II software and you can instantiate the IPs

from the IP catalog. The user logic can be any logical circuitry that are implemented using logic element

(LE) and embedded component such as DSP and internal memory in your design. In this reference

design, the user logic used is a free-running 8-bit counter. The

cnt_enter_sleep

and

cnt_exit_sleep

ports are used to ensure user logic can enter and exit sleep mode without data corruption. It is expected

for that

cnt_enter_sleep[7:0]

and

cnt_exit_sleep[7:0]

are at the same value after the user logic

enter and exit sleep mode.

gpio_pad_output

ports demonstrate tri-stated state of the GPIO when the

system is in sleep mode.

Related Information

Clock Control Block

The clock control IP core (

clk_control_altclkctrl

) is an IP provided in the Quartus II software. This

IP is used to control the clock system in the device. The GCLKs that drive through the device can be

dynamically powered down by controlling the active high

ena

signal. The

ena

port is an input to the clock

control IP block. When this IP is instantiated, select the

ena

port to enable the controls of GCLKs.

I/O Buffer

Altera GPIO Lite IP core (

altera_gpio_lite

) is implemented as an input, output, or bidirectional I/O

buffer. You can control the power down of these I/O buffers by enabling the

nsleep

port of the input

buffer and the

oe

port of the output buffer. The

oe

and

nsleep

ports are pulled low by the power

management controller design to power down the I/O buffers during sleep mode. Altera recommends you

to use a separate Altera GPIO Lite IP when some of the I/O buffer is not required to be powered down.

Internal Oscillator

Internal Oscillator IP core (

altera_in_osc

) is a free-running oscillator once you enable it. This oscillator

will be running throughout the entire power management controller design.

3-2

Clock Control Block

UG-M10PWR

2015.02.09

Altera Corporation

Power Management Controller Reference Design