Internal oscillator, I/o buffer power down – Altera MAX 10 Power User Manual

Page 10

application where the LVDS I/O needs to be powered down during the idle condition. Without touching

any buttons, the screen turns off while the camera is still powered on.

Altera provides a soft power management controller as reference design utilizing low-power features

implemented in the MAX 10 devices. You can modify the reference design based on your application. The

soft power management controller includes a simple finite state machine (FSM) to manage low-power

state mode by powering down the I/O buffer and GCLK gating during sleep mode.

All MAX 10 devices contain hardware feature for clock gating. The 10M16, 10M25, 10M40, and 10M50

devices contain hardware features for I/O power down. With hardware features, you can manage the low-

power state during sleep mode by using the soft power management controller that you define.

You can implement the power management controller in FPGA core fabric with minimum one I/O port

reserved for sleep mode enter and exit signals.

Internal Oscillator

The internal oscillator clocks the power management controller operation. The internal oscillator is

routed from flash to the core. The internal oscillator enables the power management controller to detect

the wake-up event and the sleep mode event. In order to enable the internal oscillator clock when the

power management controller is enabled, you have to set

oscena

to

1

. For the clock frequency of the

internal oscillator, refer to the MAX 10 FPGA device datasheet.

Related Information

Provides details about the MAX 10 ramp time requirements, internal oscillator clock frequency, and hot-

socketing specifications.

I/O Buffer Power Down

The MAX 10 device has a dynamic power-down feature on some of the I/O buffers that have high-static

power consumption. The dynamic power-down feature is only applicable for the I/O buffers that have

been programmed for the I/O standards in the following table.

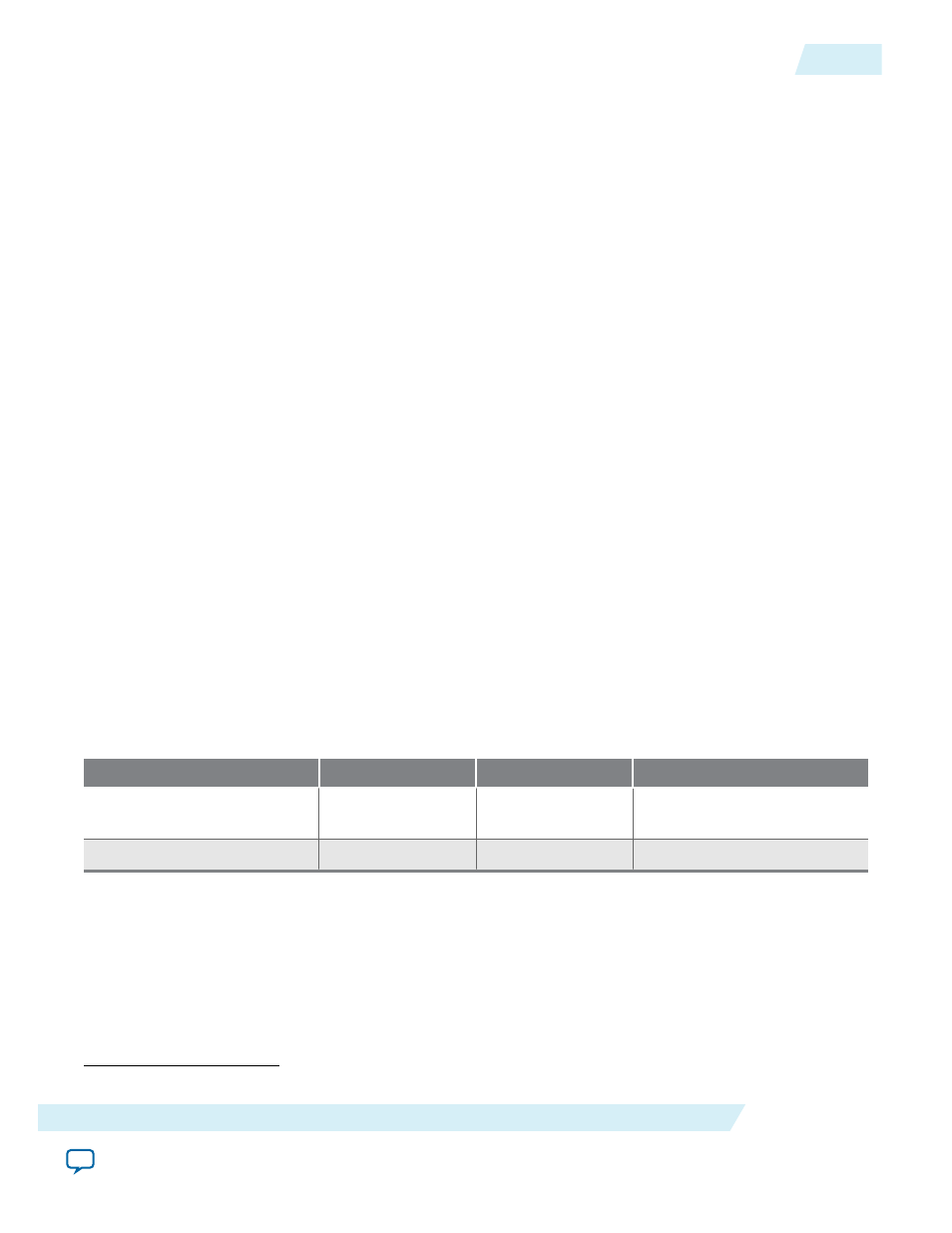

Table 2-5: I/O Buffer Power Down

I/O Buffer

I/O Standards

Control Port

Control Signal Capability

Input

SSTL, HSTL, HSUL,

and LVDS

nsleep

1 per I/O bank

(4)

Output

All I/O standards

oe

1 per I/O buffer

During power-up and configuration modes, the soft power management controller is not yet configured

and the control signals are forced to

1

(inactive). After configuration mode, when the power management

controller is activated, the power management controller will default the control signals to

1

. When

control signals are

0

, the power management controller powers down or tri-states the I/O buffers.

Subsequently the I/O is put into the sleep mode.

The MAX 10 device I/O buffers need to maintain the previous states during the sleep mode operation.

The previous states in your core logics will still remain upon exiting the sleep mode.

(4)

I/O banks 1A and 1B share one control signal.

UG-M10PWR

2015.02.09

Internal Oscillator

2-7

MAX 10 Power Management Features and Architecture

Altera Corporation