System synchronization interface, Table 4-10: ssi timing signal and functions – ADLINK PXI-2208 User Manual

Page 94

82

Operation Theory

System Synchronization Interface

SSI (System Synchronization Interface) provides the DAQ timing

synchronization between multiple cards. In DAQ-/DAQe-/PXI-

2204/2205/2206/2208 card, we designed a bi-directional SSI I/O

to provide flexible connection between cards and allow one SSI

master to output the signal and up to three slaves to receive the

SSI signal. Note that the SSI signals are designed for card syn-

chronization only and not for external devices.

In PCI form factor, there is a connector on the top right corner of

the card for the SSI. Refer to section 2.3 for the connector posi-

tion. All the SSI signals are routed to the 20-pin connector from the

FPGA. To synchronize multiple cards, users can connect a special

ribbon cable (ACL-SSI) to all the cards in a daisy-chain configura-

tion.

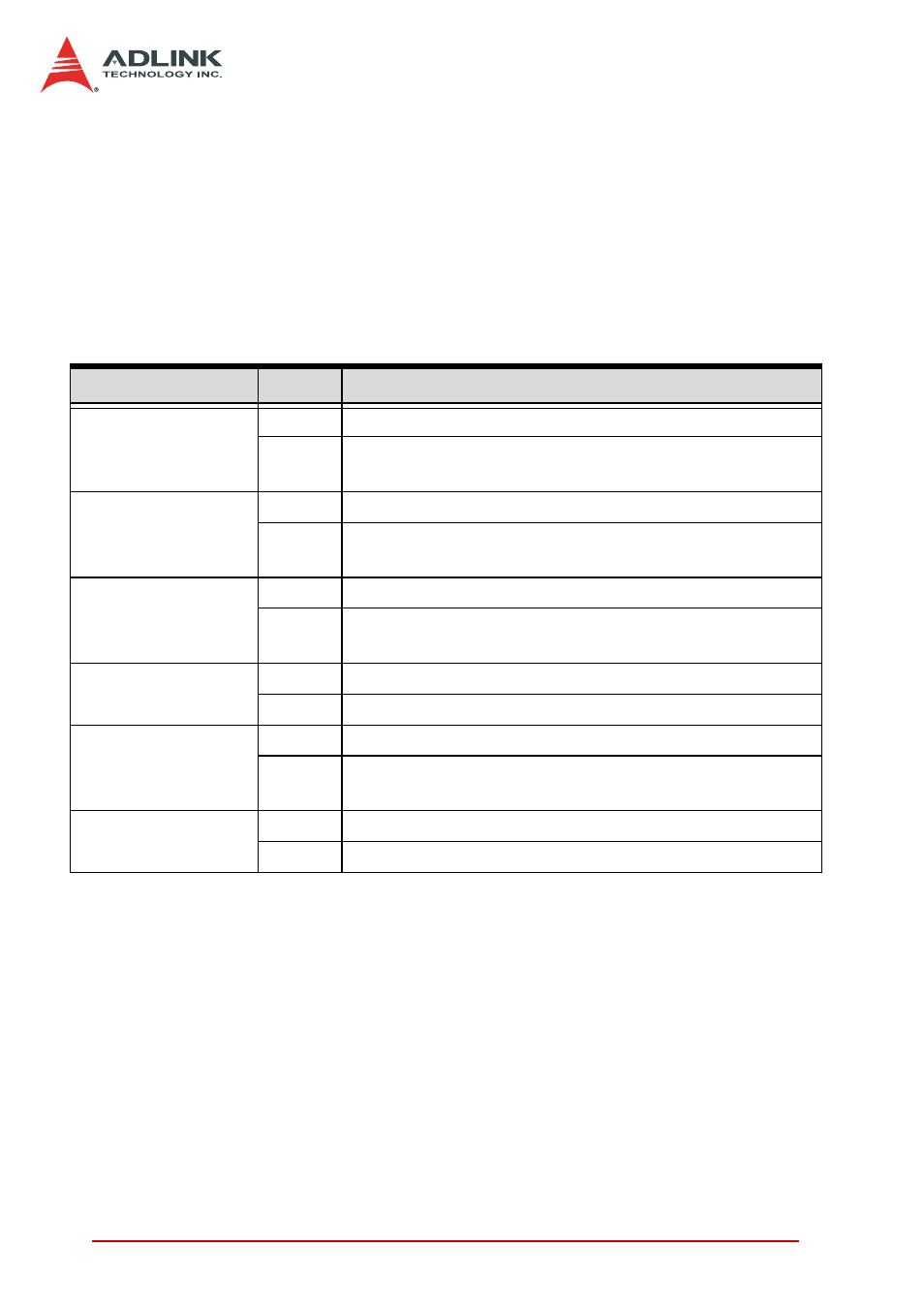

SSI Timing Signal Setting

Function

SSI_TIMEBASE

Master Send the TIMEBASE out

Slave

Accept the SSI_TIMEBASE to replace the internal

TIMEBASE signal.

SSI_ADCONV

Master Send the ADCONV out

Slave

Accept the SSI_ADCONV to replace the internal

ADCONV signal.

SSI_SCAN_START

Master Send the SCAN_START out

Slave

Accept the SSI_SCAN_START to replace the internal

SCAN_START signal.

SSI_AD_TRIG

Master Send the internal AD_TRIG out

Slave

Accept the SSI_AD_TRIG as the digital trigger signal.

SSI_DAWR

Master Send the DAWR out.

Slave

Accept the SSI_DAWR to replace the internal DAWR

signal.

SSI_DA_TRIG

Master Send the DA_TRIG out.

Slave

Accept the SSI_DA_TRIG as the digital trigger signal.

Table 4-10: SSI Timing Signal and Functions