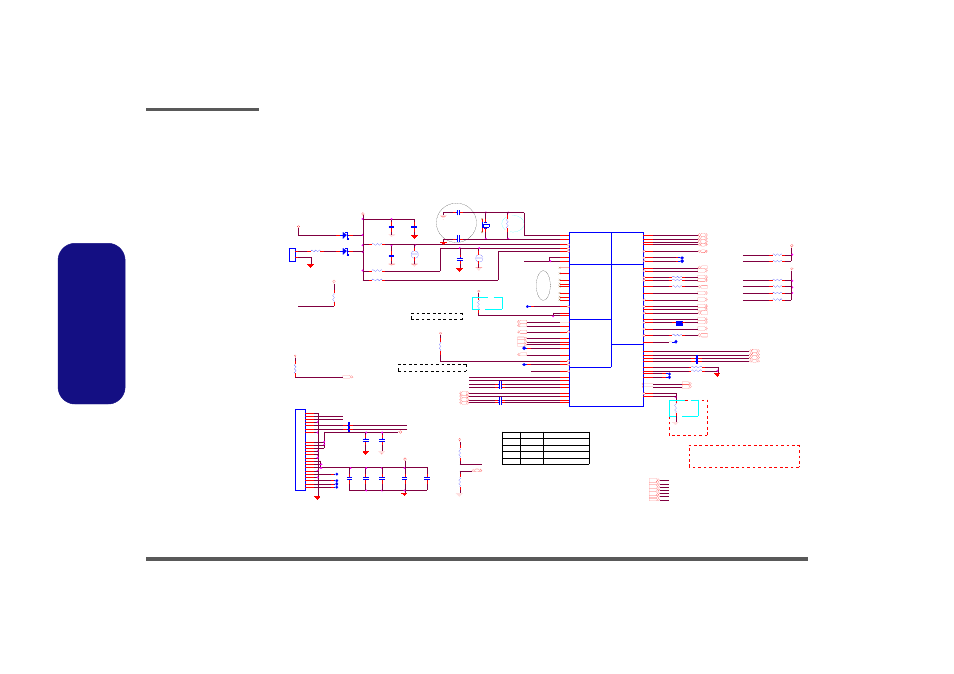

Ich9-m 1/4, sata, Sheet 13 of 42 ich9-m 1/4, sata, B.schematic diagrams – Clevo M860TU User Manual

Page 70: Sata hdd

Schematic Diagrams

B - 14 ICH9-M 1/4, SATA

B.Schematic Diagrams

ICH9-M 1/4, SATA

Sheet 13 of 42

ICH9-M 1/4, SATA

S A T A _ R X N 1 _ C

S A T A _ R X P 1 _C

17

H D A _ S D I N 3

Z 13 1 0

R T C V C C

S A TA _ L E D# 2 4

H _I N TR

2

R 4 4 7

2 4. 9 _ 1% _ 0 4

S A TA R X P 0

H D A _ D O C K _ E N #_ R

Enter XOR Chain

S A TA T X N 4 1 7

L P C_ A D 2 2 2 , 3 8

G A 20

22

A Z _S D OU T

R 2 25

2 4 . 9 _1 % _ 04

R 5 16

*1 0 mi l _ sh o rt

A Z _ R S T#

25 , 2 7 , 37

3 . 3V S

2 , 3, 5 , 9 , 1 2, 14 , 1 5, 1 6 , 1 9, 2 0 , 2 1, 2 2 , 2 3, 2 4 , 2 5, 2 6 , 2 8, 3 0 , 3 2, 3 3 , 3 5, 3 6 , 3 7, 3 8

S A T A _R X N 0 _C

I NT R U D E R #

5 V S

1 . 0 5 V S

3 . 3V

2, 1 4 , 1 5, 1 6 , 1 9, 2 1 , 2 7, 2 8 , 2 9, 3 0 , 3 1, 3 2 , 3 4, 3 6 , 3 7, 3 8

C LK _ S A T A # 1 8

S A T A _R X N 4 _C

S A T A _ TX P 1 _ C

Descr iption

5 V S

1 6, 1 7 , 2 1, 2 3 , 2 5, 2 6 , 2 8, 3 3 , 3 7, 3 8

H _F E R R # 2

H _I G N N E # 2

S A T A _R X P 4_ C

R 5 3 5

*1 K _ 0 4

I C H _ T P 12

C 1 5 7

. 1 u_ 1 6 V _0 4

1 . 5V S

3 , 9, 1 6 , 2 1, 2 3 , 3 3, 3 6

S R T C R S T #

C 2 5 8

1 u _6 . 3 V _ 04

RSVS

S A T A _ T XP 4 _ C

P M _T H R MT R I P # 2 , 5

K B C _R S T C # 2 2

C 1 5 8

. 1u _ 1 6V _ 0 4

H _P W R GD

2

Z 1 3 01

C 4 7 5

. 1 u_ 1 6V _0 4

S A T A _R X P 0_ C

A Z _S D I N 2

R 5 15

5 4. 9 _ 1 %_ 0 4

RT

C

LA

N /

GL

AN

IH

DA

SA

TA

LP

C

CP

U

U 1 5A

I C H 9 M R E V 1. 0

C 2 3

C 2 4

B 2 2

C 2 2

E 2 5

C 1 3

F 1 4

G1 3

D 1 4

D 1 3

D 1 2

E 1 3

A F 6

A H 4

A E 7

A F 4

A G 4

A H 3

A G 5

A G 8

A J 1 6

A H 1 6

A F 1 7

A G1 7

A H 1 3

A J 1 3

A G1 4

A F 1 4

A H 1 8

A J 18

A J 7

A H 7

K 5

K 4

L 6

K 2

J 3

J 1

K 3

N 7

A J 27

A J 25

A E 2 3

A J 26

A D 2 2

A F 2 5

A E 2 2

A G2 5

L 3

A F 2 4

A F 2 3

A H 2 7

A G2 6

A 2 5

B 1 0

B 2 7

B 2 8

A E 5

A G1 2

A H 1 1

A F 1 2

A J 11

A G2 7

A G 7

A E 8

A 2 2

A H 9

A J 9

A E 1 0

A F 1 0

F 2 0

R T CX 1

R T CX 2

I N T V R M E N

I N T RU D E R #

GL A N _ C LK

LA N_ R S T S Y N C

LA N_ R X D 0

LA N_ R X D 1

LA N_ R X D 2

LA N_ TX D 0

LA N_ TX D 1

LA N_ TX D 2

H D A _B I T _ C L K

H D A _S Y N C

H D A _R S T #

H D A _S D I N 0

H D A _S D I N 1

H D A _S D I N 2

H D A _S D OU T

S A T A LE D #

S A T A 0R X N

S A T A 0R X P

S A T A 0T X N

S A T A 0T X P

S A T A 1R X N

S A T A 1R X P

S A T A 1T X N

S A T A 1T X P

S A TA _ C L K N

S A T A _C L K P

S A T A R B I A S #

S A T A R B I A S

F W H 0 / LA D 0

F W H 1 / LA D 1

F W H 2 / LA D 2

F W H 3 / LA D 3

L D R Q0 #

L D R Q 1 #/ G P I O2 3

F W H 4 / L F R A M E #

A 2 0G A T E

A 2 0 M#

D P R S T P #

D P S L P #

F E R R #

C P U P W R GD

I GN N E #

I N I T #

I N TR

R C I N #

S MI #

N M I

S T P C L K #

TH R M TR I P #

R T CR S T #

GP I O 56

GL A N _ C OMP O

GL A N _ C OMP I

H D A _S D I N 3

S A T A 4 T XN

S A TA 4 R XN

S A TA 4 T X P

S A T A 4R X P

T P 1 2

H D A _D OC K _E N # / GP I O 33

H D A _D OC K _R S T #/ G P I O3 4

LA N1 00 _ S L P

S A TA 5 R XN

S A T A 5R X P

S A T A 5 T XN

S A TA 5 T X P

S R T C R S T #

1 . 05 V S

2, 3 , 4 , 5 , 9, 1 6 , 1 8, 3 3

H _A 2 0 M#

2

H _ DP R S TP #

JC B A T 1

8 5 20 5 -0 2R

1

2

AZ_SDOUT

3 . 3V S

C 1 33

10 u _1 0 V _ 08

R 4 91

8 . 2K _ 0 4

S A T A T XP 0

S A T A T XP 1

Z 13 1 7

L P C _ D R Q0 #

3 . 3 V S

I C H _I N TV R ME N

C 1 8 9

0 . 01 U _X 7 R _ 0 4

C 2 6 8

1 2 p_ 5 0V _0 4

S A T A _ TX N 0_ C

3. 3V S

Z 13 1 1

RT C R S T #

DVT

1

Z 13 1 6

R 2 27

*5 6 _0 4

20m i ls

S A TA TX N 1

1 7

Z 1 3 13

J OP E N 2

* OP E N _1 0 mi l -1 MM

1

2

A Z _ S Y N C

25 , 2 7 , 37

S A TA R X N 0

R 53 3

* 10 K _ 0 4

H _I N I T #

2

C 2 7 5

1 2 p_ 5 0V _0 4

R 2 28

5 6_ 0 4

R 5 29

*5 6 _0 4

1

S A TA _L E D #

C L K _ S A TA

18

S A T A _ R X N 0 _ C

SATA HDD

1 . 5V S

I C H _ GP I O 23

A Z _ S D I N 1

2 7

ICH_ TP3

JS A T A 2

C 1 6 65 6 -12 2 0 4-L

S 1

S 2

S 3

S 4

S 5

S 6

S 7

P 1

P 2

P 3

P 4

P 5

P 6

P 7

P 8

P 9

P 1 0

P 1 1

P 1 2

P 1 3

P 1 4

P 1 5

S A T A TX P 4

Z 1 3 06

D 3 8 S C S 7 51 V -4 0

A

C

1

H D A _ D OC K _R S T#

R 1 6 7

2 0 K _1 % _ 04

3 . 3 V S

HDA_SYNC:PCI- E Conf . 1 bit 0

RT C _ X 2

54 .9 _1% n eed s to pl ac ed wi th in 2" of I CH 8, 56

Oh m mus t be pl ac ed wi thi n 2" of 2 4.9 _1 % w/o

st ub .

L P C_ A D 1 2 2 , 3 8

C 1 9 6

0 . 01 U _X 7 R _ 0 4

PVT

C 67 4

0. 0 1 U _ X 7R _ 04

R 1 81

3 3 2 K _1 % _ 06

P I N G N D 1 ~ 2 = G N D

1

H _S T P C LK # 2

S A T A _ R X P 0 _C

S A TA _ R X P 4 _ C 1 7

Flash Descriptor Secur it y Ove rride Strap

C 2 59

1u _ 6. 3V _ 0 4

10m il s

H _N MI

2

G A 2 0

Z 1 3 07

GL A N _C OM P

C LK _ S A T A

D 3 9 S C S 7 51 V -4 0

A

C

R 2 21

0 _ 04

Layout note:

R TC V C C

R 1 7 5

1 0M _0 4

C 4 9 7

0. 0 1 U _ X 7R _ 04

R 5 19

0 _ 04

R 5 28

5 6_ 0 4

H _ DP S L P #

C LK _ S A T A #

K B C_ R S T C #

Z 13 0 2

A Z _ S D I N 2

3 7

H _ F E R R #

S A TA TX N 0

S A T A _ T XN 4_ C

S A T A _ R I B A S _P N

Z 13 1 8

S A TA TX P 1

1 7

H _S M I #

2

R 66 0

0 _0 4

0

X 2

3 2 . 76 8 K H z

1

4

3

2

C 5 66

1u _ 6. 3V _ 0 4

C 13 5

1 0 u_ 1 0 V _0 8

R TC CL EA R

C 4 9 6

0. 0 1 U _ X 7R _ 04

H _D P R S T P # 2 , 5, 3 5

H _D P S L P # 2

S A T A _ TX N 1_ C

S A T A _ R X P 1 _C

S A T A _ R X N 1 _ C

17

A Z _ S D I N 0

2 5

LP C _A D 3 22 , 3 8

A Z _ S D OU T

2 5, 2 7 , 37

I C H _ I N T V R ME N

I C H _ GP I O 56

Z 1 3 04

0

V D D 3

2 , 1 9, 2 2 , 2 4, 2 9 , 3 2, 3 3 , 3 4, 3 7

S A TA _ R X N 4_ C

17

L P C_ F R A ME # 2 2, 3 8

R 4 2 4

1K _0 4

P M_ TH R M TR I P #

S A T A _ TX P 0 _ C

C 55 9

. 1u _ 1 6V _ 0 4

S A T A T XN 1

SATA

? TX/RX? ? ? ? ? Connector

Within 500mil

A Z _ B I TC L K

2 5 , 27 , 3 7

C 67 3

0. 0 1 U _ X 7R _ 04

R 4 5 6

*1 K _ 0 4

0

0

3 . 3 V S

S A T A TX N 4

J OP E N 1

* OP E N _1 0 m il -1 MM

1

2

Z 1 3 12

R 1 6 8

2 0K _ 1 % _0 4

S A TA TX P 0

RT C _ X 1

T PM CL EA R

C 4 9 8

0 . 01 U _X 7 R _ 0 4

Z 1 3 08

S A TA T X P 4 17

S A T A T XN 0

C 1 34

1 0 u _1 0 V _ 08

Set PCIE port conf ig bit 1

V DD 3

Z 13 1 5

D V T

C 4 7 6

*1 0 u_ 1 0 V _0 8

R 2 22

5 6 _0 4

LP C _A D 0 22 , 3 8

R2 2 4

*1 0 K _ 04

R 4 69

1 0K _ 0 4

I C H _ T P 3

1 5

Z 1 3 05

R 4 5 1

1 M_ 0 4

R 65 9

0 _0 4

C 4 9 9

0 . 01 U _X 7 R _ 0 4

Nor ma l Oper ation (Def ault)

R T C V C C

16

DVT:Change to 12P