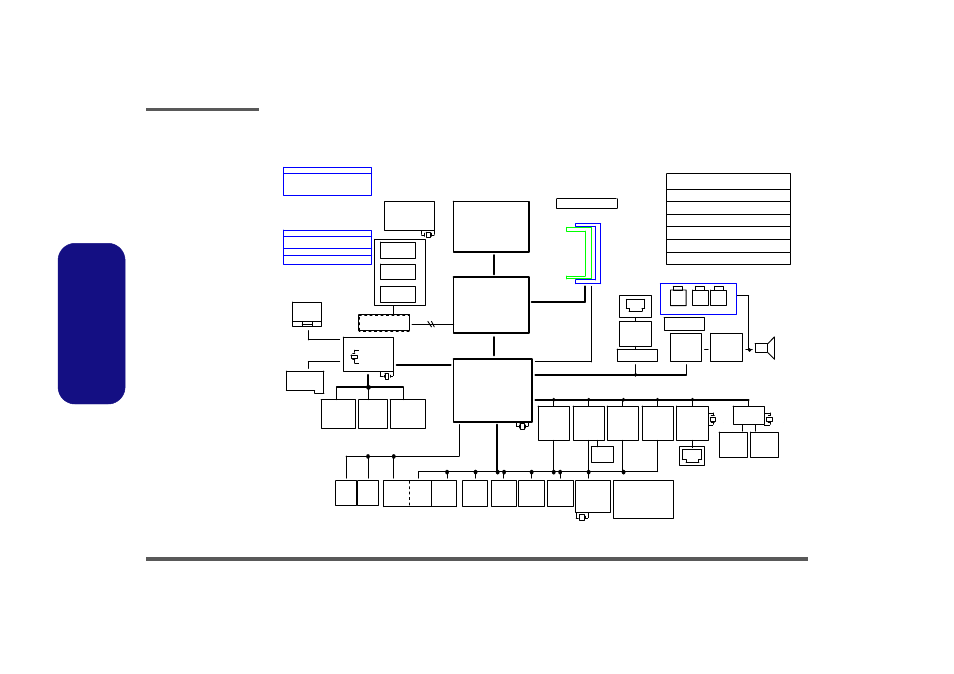

System block diagram, Sheet 1 of 42 system block diagram, B.schematic diagrams – Clevo M860TU User Manual

Page 58: Schematic diagrams b - 2 system block diagram, Clevo m860tu system block diagram, Penryn, 676 bga, 1329 ball fcbga, 478 ufcpga, Processor

Schematic Diagrams

B - 2 SYSTEM BLOCK DIAGRAM

B.Schematic Diagrams

SYSTEM BLOCK DIAGRAM

Sheet 1 of 42

SYSTEM BLOCK

DIAGRAM

D DR 3 S DR AM S OC KET

S O- DIM M1

5. 1 C HA NN EL OU T

APA 20 56

Mi ni C ARD

14.318 MHz

L AN

INT.

SPK

US B0

F ING ER P RI NT ER BO AR D

USB_Conn.

M EM ORY T ER MI NA TIO NS

SIM Ca rd

3 G

US B7

Penryn

5V S, 3VS ,1 .5 VS ,1. 05 VS

T OU CH

P AD

RJ-11

USB_Conn.

SO -D IM M2

676 BGA

SYS TE M SM BUS

( M/ B s ide )

CARD

READER

U SB 10

1. 5V ,VT T_ ME M

C LI CK BO AR D

Mi ni CA RD

VC OR E

RTL8111C

C CD

M MC/ SD /M S/M S Pr o

PC IE

P OWE R BO TT OM LE D

A SC7 52 5

JMB 38 0

33 MHz

MD C CO NN .

T HE RMA L

S EN SOR

24 MHz

32.768

KHz

S MA RT

F AN

DDR II I

S AT A

O DD

HDMI

MIC

IN

NE W

CA RD

US B2 .0

U SB 6

S OC KE T

US B2

IT 851 2

S OCK ET

GM P owe r

e- SAT A

SOUTH BRIDGE

M in i C AR D

7 IN 1

LVDS

800/1066 MHz

1329 ball

FCBGA

CLEVO M860TU System Block Diagram

LP C

US B3

B OTT OM

RJ-45

US B5

12 MHz

D MI

S oc ket P

M XM -II I VG A

D AU GHT ER C ARD

A ZAL IA

C ODE C

478 uFCPGA

SAT A

HDD

SO CKE T

CLOCK GEN.

U SB 4

ICS 9L PR3 95

SMA RT

BAT TE RY

I NT . K/B

AU DIO

AM P.

Hot Key & Click

Connector

In te l

Ca nt ig a

X4

US B1

S ATA -1 50

24.576

MHz

DVI/RGB

HP

OUT

10 MHz

25 MHz

A ZA LI A

M DC

M OD UL E

BT

US B8 ,9

R obs on

E C S MB US

SPDIF

OUT

IEEE

1394

F SB

PROCESSOR

PC I- E x1 6

EC

VI N, VA ,V B

Fi ng er

Pr in ter

BU TT OM BO AR D

667/800/1066 MHz

NORTH BRIDGE

AZ AL IA L INK

S RS

ICH9M

3. 3V M,1 .8 VS ,1 .05 VM

WL AN

100 MHz

SY S5 V,S YS 3V ,V DD3 ,V DD 5, 3V ,5V

32.768

KHz

ALC 66 2

REALTEK