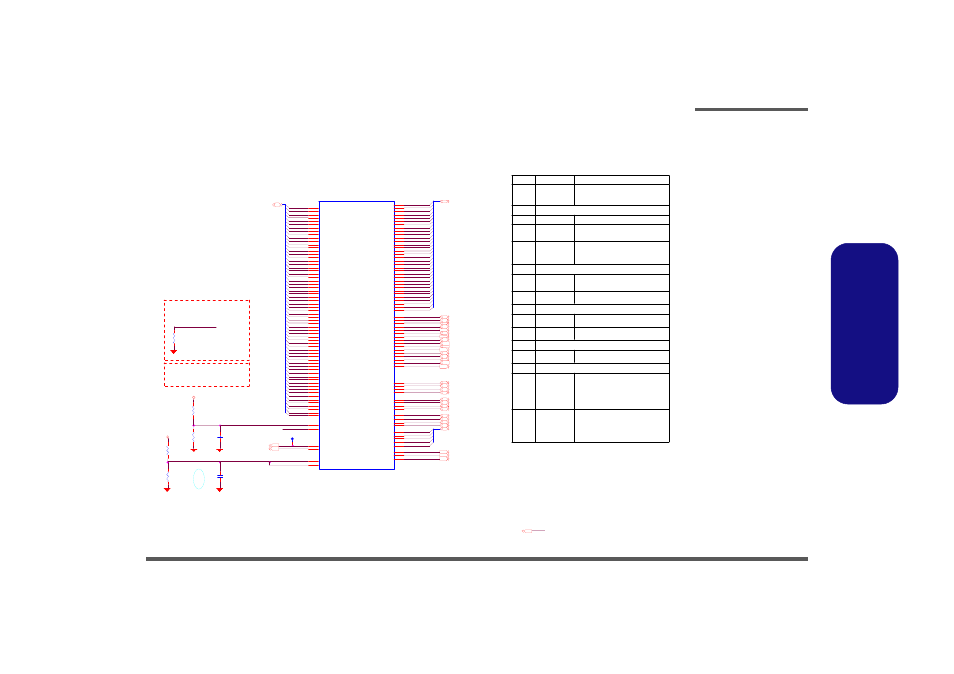

Cantiga 1/6, host, Sheet 4 of 42 cantiga 1/6, host, B.schematic diagrams – Clevo M860TU User Manual

Page 61: Schematic diagrams cantiga 1/6, host b - 5, Host

Schematic Diagrams

Cantiga 1/6, Host B - 5

B.Schematic Diagrams

Cantiga 1/6, Host

Sheet 4 of 42

Cantiga 1/6, Host

H _D # 4 3

PCIe Gr aphics Lan e

H _D # 9

CFG6

H _ C P U S L P #

2

H _ A # 1 2

Low = DMI x2

High = DMI x4 (Defa ult)

10mils

H _ A # 9

H _D R D Y # 2

H _B R 0 #

2

H _D # 1

H _D # 7

1 . 0 5 V S

H _D I N V #1 2

H _R E Q #[ 4 : 0 ] 2

H _ A # 1 4

Digital Display Port

(SDVO/ DP/iHDMI)

Con curr ent w ith

PCIe

H _ A # 2 7

Z 0 4 0 1

H _ A # 3 4

H _D # 2 0

H _D # 5 0

H _D # 2 8

H _B P R I #

2

C L K _ MC H _ B C LK

18

H _D # 1 5

Low = Only dig ita l display port ( SDVO/DP/iHDMI)

o r PCIe is o perat ion al ( def ault)

High = Digita l d isp lay port ( SDVO/DP/iHDMI)

a nd PCIe a re op erating s imultaneo usly

v ia t he PEG por t

H _ A # 2 4

DMI Lane Rever sal

H _ A # 8

H _D # 1 7

H _D # 4 5

R 9 5

1 00 _ 1 % _0 4

FSB Dy namic ODT

H _H I T M#

2

H _D # 5 8

H _D # 3 9

H _D # 3 3

H _ A # 3 3

CFG11

Low = The ITPM Host Inter face is e nabled

High = Disabled ( Def ault)

H _D # 1 8

H _D # 5 5

CFG12

H _ D # [ 63 : 0 ]

2

H _D # 0

H _D # 5 4

1 . 0 5V S

H _D # 5 6

Co nfigur ation

H _ R E Q# 4

Res erved

H _ A # 2 6

10 mils wide, 20 mils spacing

Low = Nor mal opera tion (Default) :

L ane Nu mb ered in Or der

High = Rever se Lane s

DMI x 4 mode [( G)MCH->ICH]:

( 3->0 , 2-> 1, 1->2 and 0- >3)

DMI x 2 mode [( G)MCH->ICH]:

( 3->0 , 2->1 )

Low = ALLZ mod e enabled

High = Disabled (d efault)

H _A D S T B # 0 2

H _D # 3 4

H _D # 3 2

H _D S T B N #0 2

H _ A # 3 5

H _D # 1 4

Low = XOR mo de enab led

High = Disabled (d efault)

H _ A # 5

H _D # 4 9

H _ A # 1 1

Pin Na me

H _D S T B N #1 2

H _D # 5

H _D # 2 3

H _D # 2 5

H _ A # 2 5

Layout Notice:

ALLZ

Low = Reve rse L anes, 15 ->0, 1 4->1 e tc

High = Normal ope ration ( defa ult ):

L ane Numbered in Or der

H _D # 4 8

H _ R E Q# 3

H _D # 1 3

H _D # 1 0

H _D # 3 6

H _R S # 1

2

M C H _H S W I N G

CFG10

H _D # 1 6

DMI x2 Select

H _D S T B P # 2 2

H _ A # 1 9

H _R S # 0

2

H _ A # 1 6

H _D # 2 4

Res erved

CFG9

H _D # 3

H _ C P U R S T #

2

H _ A # 2 3

H _ A # 6

H _D # 6 0

H _ A # 3 2

CFG7

H _ A # 3 1

H _A #[ 3 5 : 3 ] 2

MCH_HSWING a 10 mils traces

and 20 mils spacing

H _D S T B N #3 2

H _ A # 1 3

H _D # 3 7

Res erved

CFG8

H _D # 2 1

C 1 36

0 . 1 u _ 10 V _ 0 4

H _T R D Y # 2

H _D # 1 2

H _ A # 7

H _ A # 2 2

CFG4: 3

H _A D S #

2

H _ A # 1 5

H _D I N V #0 2

H _D # 2

H _D P W R # 2

H _ R E Q# 2

H _D # 1 1

Res erved

FSB Fr eguency

H _L O C K # 2

H _D # 3 0

H _D # 2 7

H _D S T B P # 3 2

C 1 28

* 0 . 1u _ 1 0 V _0 4

CFG20

H _ A # 2 8

H _D # 6

HOST

U 2 5 A

C A N T I GA

P 1 6

R 1 6

N 1 7

M 1 3

E 1 7

P 1 7

F 1 7

G 2 0

B 1 9

J 1 6

E 2 0

H 1 6

J 2 0

L 1 7

A 1 7

B 1 7

L 1 6

C 2 1

J 1 7

H 2 0

A 1 4

B 1 8

K 1 7

C 1 5

F 1 6

H 1 3

C 1 8

M 1 6

J 1 3

H 1 2

B 1 6

G 1 7

A 9

F 1 1

G 1 2

A H 6

C 12

A H 7

F 2

F 1 3

B 1 3

G8

M9

L6

N 10

A A 8

A A 2

A E 11

D 4

H 3

B 1 0

M 11

J1

J2

N 12

J6

P 2

L2

R 2

N 9

F 8

M5

J3

N 2

R 1

N 5

N 6

P 13

N 8

L7

E 6

M3

Y 3

A D 14

Y 6

Y 10

Y 12

Y 14

Y 7

W 2

G2

Y 9

A A 13

A A 9

A A 11

A D 11

A D 10

A D 13

A E 12

A E 9

H 6

A D 8

A A 3

A D 3

A D 7

A E 14

A F 3

A C 1

A E 3

A C 3

H 2

A E 8

A G2

A D 6

F 6

E 9

J 8

L 3

Y 1 3

Y 1

J 1 1

F 9

L 1 0

M 7

A A 5

A E 6

L 9

M 8

A A 6

A E 5

A 11

B 11

C 9

H 9

E 1 2

H 1 1

B 1 5

K 1 3

B 1 4

B 2 0

F 2 1

K 2 1

L 2 0

C 5

E 11

E 3

B 6

F 1 2

C 8

H _ A # _1 0

H _ A # _1 1

H _ A # _1 2

H _ A # _1 3

H _ A # _1 4

H _ A # _1 5

H _ A # _1 6

H _ A # _1 7

H _ A # _1 8

H _ A # _1 9

H _ A # _2 0

H _ A # _2 1

H _ A # _2 2

H _ A # _2 3

H _ A # _2 4

H _ A # _2 5

H _ A # _2 6

H _ A # _2 7

H _ A # _2 8

H _ A # _2 9

H _ A #_ 3

H _ A # _3 0

H _ A # _3 1

H _ A #_ 4

H _ A #_ 5

H _ A #_ 6

H _ A #_ 7

H _ A #_ 8

H _ A #_ 9

H _A D S #

H _ A D S T B #_ 0

H _ A D S T B #_ 1

H _ B N R #

H _B P R I #

H _ B R E Q#

H P L L _ C L K #

H_ C P U R S T#

H P L L _ C L K

H_ D # _ 0

H _ R E Q #_ 2

H _ R E Q #_ 3

H_ D # _ 1

H_ D # _ 1 0

H_ D # _ 2 0

H_ D # _ 3 0

H_ D # _ 4 0

H_ D # _ 5 0

H_ D # _ 6 0

H_ D # _ 8

H_ D # _ 9

H _ D B S Y #

H_ D # _ 1 1

H_ D # _ 1 2

H_ D # _ 1 3

H_ D # _ 1 4

H_ D # _ 1 5

H_ D # _ 1 6

H_ D # _ 1 7

H_ D # _ 1 8

H_ D # _ 1 9

H_ D # _ 2

H_ D # _ 2 1

H_ D # _ 2 2

H_ D # _ 2 3

H_ D # _ 2 4

H_ D # _ 2 5

H_ D # _ 2 6

H_ D # _ 2 7

H_ D # _ 2 8

H_ D # _ 2 9

H_ D # _ 3

H_ D # _ 3 1

H_ D # _ 3 2

H_ D # _ 3 3

H_ D # _ 3 4

H_ D # _ 3 5

H_ D # _ 3 6

H_ D # _ 3 7

H_ D # _ 3 8

H_ D # _ 3 9

H_ D # _ 4

H_ D # _ 4 1

H_ D # _ 4 2

H_ D # _ 4 3

H_ D # _ 4 4

H_ D # _ 4 5

H_ D # _ 4 6

H_ D # _ 4 7

H_ D # _ 4 8

H_ D # _ 4 9

H_ D # _ 5

H_ D # _ 5 1

H_ D # _ 5 2

H_ D # _ 5 3

H_ D # _ 5 4

H_ D # _ 5 5

H_ D # _ 5 6

H_ D # _ 5 7

H_ D # _ 5 8

H_ D # _ 5 9

H_ D # _ 6

H_ D # _ 6 1

H_ D # _ 6 2

H_ D # _ 6 3

H_ D # _ 7

H _ D E F E R #

H _D I N V #_ 0

H _D I N V #_ 1

H _D I N V #_ 2

H _D I N V #_ 3

H _ D P W R #

H _ D R D Y #

H _ DS T B N #_ 0

H _ DS T B N #_ 1

H _ DS T B N #_ 2

H _ DS T B N #_ 3

H _ D S TB P #_ 0

H _ D S TB P #_ 1

H _ D S TB P #_ 2

H _ D S TB P #_ 3

H_ A V R E F

H_ D V R E F

H _ T R D Y #

H _ H I T #

H _H I T M#

H _L O C K #

H _ R E Q #_ 0

H _ R E Q #_ 1

H _ R E Q #_ 4

H _ A # _3 2

H _ A # _3 3

H _ A # _3 4

H _ A # _3 5

H_ S W I N G

H_ C P U S L P #

H_ R C OM P

H_ R S #_ 0

H_ R S #_ 1

H_ R S #_ 2

H _D E F E R # 2

H _D # 4

H _D # 5 3

H _A D S T B # 1 2

H _ A # 2 9

10mils

R 9 1

1 K _ 1 % _0 4

H _D # 6 3

H _D # 6 1

H _D B S Y # 2

H _D # 5 7

H _D # 6 2

R 10 4

2 4. 9_ 1 % _ 04

R 9 0

2 K _ 1 % _0 4

Res erved

H _H I T #

2

H _D # 2 6

CFG15 :14

Layout Notice:

PCIe Lo opback

enable

H _D S T B N #2 2

H _ A # 1 8

H _D # 5 1

R 9 6

2 21 _ 1 % _0 4

CFG18 :17

H _D S T B P # 1 2

CFG2: 0

H _D # 4 0

H _D # 4 7

H _ A # 2 1

CFG13

H _ A # 3

H _D # 1 9

CFG16

Low = Dyna mic ODT disabled

High = Dynamic ODT enabled ( defa ult)

H _ R E Q# 0

H _D # 2 2

1. 0 5 V S

2 , 3 , 5 , 9 , 1 3, 16 , 1 8 , 3 3

H _ A # 1 7

H _D # 3 1

C LK _M C H _ B C L K # 1 8

CFG5

H _D S T B P # 0 2

H _D # 4 6

H _ R E Q# 1

M C H _ H R C O MP

Low = Enabled

High = Disabled (d efault)

H _D # 5 9

H _D # 3 5

H _D # 8

000 = 10 66

010 = 80 0

011 = 66 7

Ot hers = Rese rved

D VT: Del C127

H _D # 3 8

Low = In tel Ma nagement Engine Cr ypto Transp ort Lay er

Secur ity (TLS) c iph er suite w ith no c onfidentiality

High = Intel Manag ement Engine Cry pto TLS cipher suite

w ith conf id entiality ( def ault)

H _D # 5 2

H _ A # 3 0

H _B N R #

2

H _ A # 4

In tegra ted Tr usted

Platfor m Module(ITPM)

Hos t In terf ace

100mil

H _D # 4 4

H _D # 4 1

M C H _H R C OM P

XOR

H _D # 4 2

In tel Ma nagement

Engine Crypt o

Str ap

H _R S # 2

2

H _D I N V #2 2

Str ap Description

CFG19

H _D I N V #3 2

H _ A # 2 0

H _ A # 1 0

H _D # 2 9