10 bist, Bist, Table 8: bist run times – Maxim Integrated 78Q8430 Software Driver User Manual

Page 45

UG_8430_004

78Q8430 Software Driver Development Guidelines

Rev. 1.0

45

10 BIST

Use the following procedure to run the built in self-check for the embedded memories:

STEP 1: Set the BCR BIST Enable bit.

STEP 2: Set the BCR BIST Mode field for the desired BIST test mode.

STEP 3: Set the BCR BIST Start bit.

This bit initiates the currently selected BIST test and then auto-clears. For BYPASS test mode this

step is necessary to go into BYPASS. Once in BYPASS mode, BYPASS mode is maintained until a

new BIST Mode is selected and the BIST Start bit is set again to initiate the new mode.

STEP 4: Poll BCR in order to determine if the current BIST test is done.

When the selected test is complete, the BCR Pass bit or Fail bit will be set. If they are both clear, the

currently selected BIST test is still in progress.

Use BYPASS mode when a manual test is needed. Using BYPASS mode to test the RAM is not covered

here. For reference purposes, in BYPASS Mode, the RAM Data is read or written using the BBDR

register. If auto-incrementing is selected, the address increments after each BYPASS RAM cycle (read or

write of BBDR register). The current address pointer can be determined by reading back the RAM

Address contained in the BCR RAM Address field.

In BYPASS mode the Pass bit is set immediately. It is up to the host to determine the pass/fail criteria.

For best fault coverage, the recommended test mode sequence is FILL 1, wait 10 ms, READ 1,

PATTERN, FILL 0, wait 10 ms, READ 0. The 10 ms delays are needed to catch slow bit failures.

As a reference point the following times were measured in simulation with a 100 Mhz system clock.

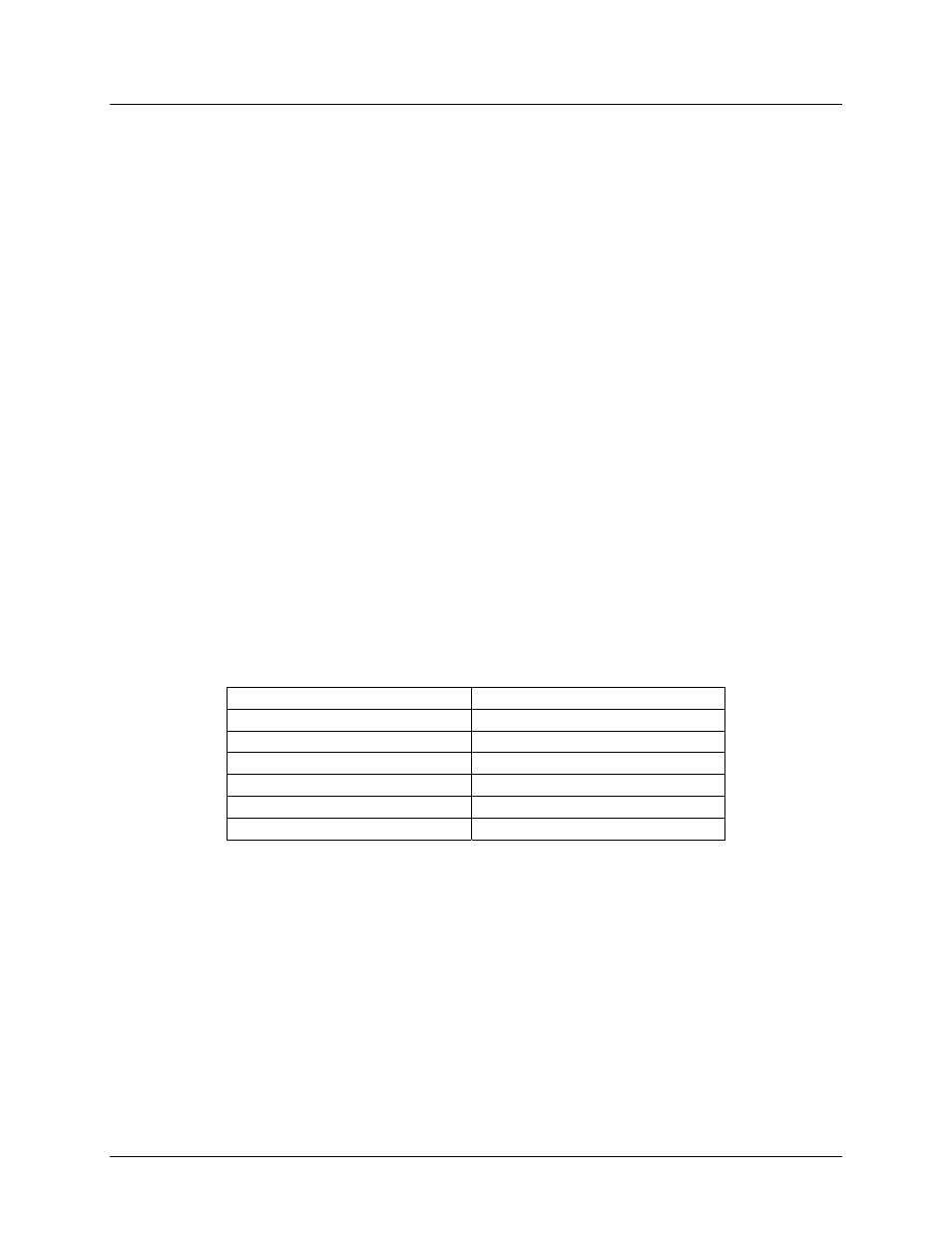

Table 8: BIST Run Times

BIST Mode

Time to Complete @ 100 MHz

PATTERN (001)

6300

us

FILL 0

(010)

85 us

READ 0

(011)

170 us

FILL 1

(100)

85 us

READ 1

(101)

170 us

BYPASS*

(110)

0 us