3 transmit pause, Transmit pause, Specify pause frame – Maxim Integrated 78Q8430 Software Driver User Manual

Page 10: Specify pause time

78Q8430 Software Driver Development Guidelines

UG_8430_004

Disabling Hardware Jabber Protection

Use the following procedure to disable hardware jabber protection:

STEP 1: Set the MCR Jumbo OK bit.

3.3 Transmit

PAUSE

This section describes the procedures used to access the automatic immediate PAUSE transmission

feature.

3.3.1 Specify PAUSE Frame

When the PAUSE watermark is reached, the 78Q8430 automatically transmits a PAUSE frame. Section

describes how to set the PAUSE watermark level. Use the following procedure to write the PAUSE

frame to QUE 2:

STEP 1: Write to QUE 2 PCWR.

Writing to this register sets the ID and transmission options for the frame and initializes the write logic

for QUE 2. The driver should assign a unique ID number to each transmitted frame. When the write

logic is initialized, it triggers an under-run interrupt for QUE 2 if the previous frame has not been

completed. This has the effect of aborting the previous frame.

STEP 2: Write to QUE 2 PSZR.

Writing to PSZR indicates to the QUE 2 write logic how many bytes to expect. For example, if the

part is operating in 32-bit bus mode and the byte count is not an even multiple of four, the write logic

uses the size value to determine how many bytes in the last write are valid. If the host attempts to

write an extra word past the end of the programmed size, an overrun interrupt results.

STEP 3: Write the frame data to QUE 2 TDR.

Each successive write to TDR adds the data to QUE 2.

STEP 4: Read the transmit status from TPSR.

Reading TPSR reads status words from the top of a 128 word deep FIFO. One status word is added

to the FIFO for each transmitted frame. If the software does not read the status words for transmitted

frames from the FIFO, it eventually fills to capacity at which time any new status words are dropped

while the FIFO retains the oldest ones.

3.3.2 Specify PAUSE Time

It may be more convenient for the application to simply specify the PAUSE time rather than the entire

PAUSE frame. Use the following procedure to specify the PAUSE time in milliseconds:

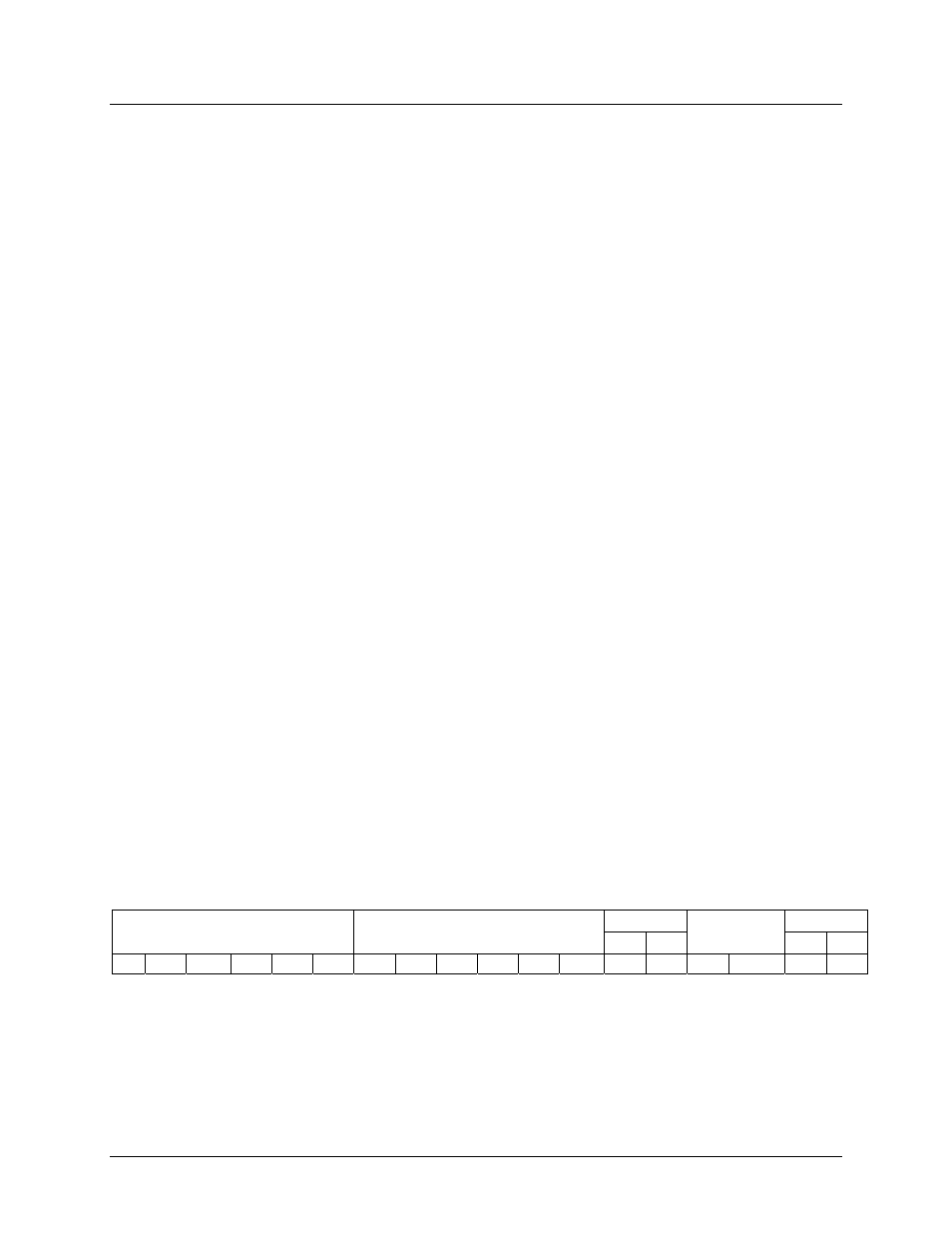

STEP 1: Assemble the following frame in host memory.

Len/Typ Time

Destination Address

Source Address

Hi Lo

PAUSE

OPCODE

Hi Lo

01 80 C2 00 00 01 ?? ?? ?? ?? ?? ?? 88 08 00 01 ?? ??

STEP 2: Insert the host MAC address in the Source Address field.

STEP 3: Insert the desired 16-bit PAUSE time into the Time field.

The most significant byte is placed in the Hi field and the least significant byte in the Lo field.

STEP 4: Write to QUE 2 PCWR to set the ID and transmission options.

Writing to this register initializes the write logic for QUE 2. When the write logic is initialized, it

10

Rev.

1.0