Digilent Pegasus Board User Manual

Page 10

Pegasus Reference Manual

Digilent, Inc. ™

www.digilentinc.com

Page

10

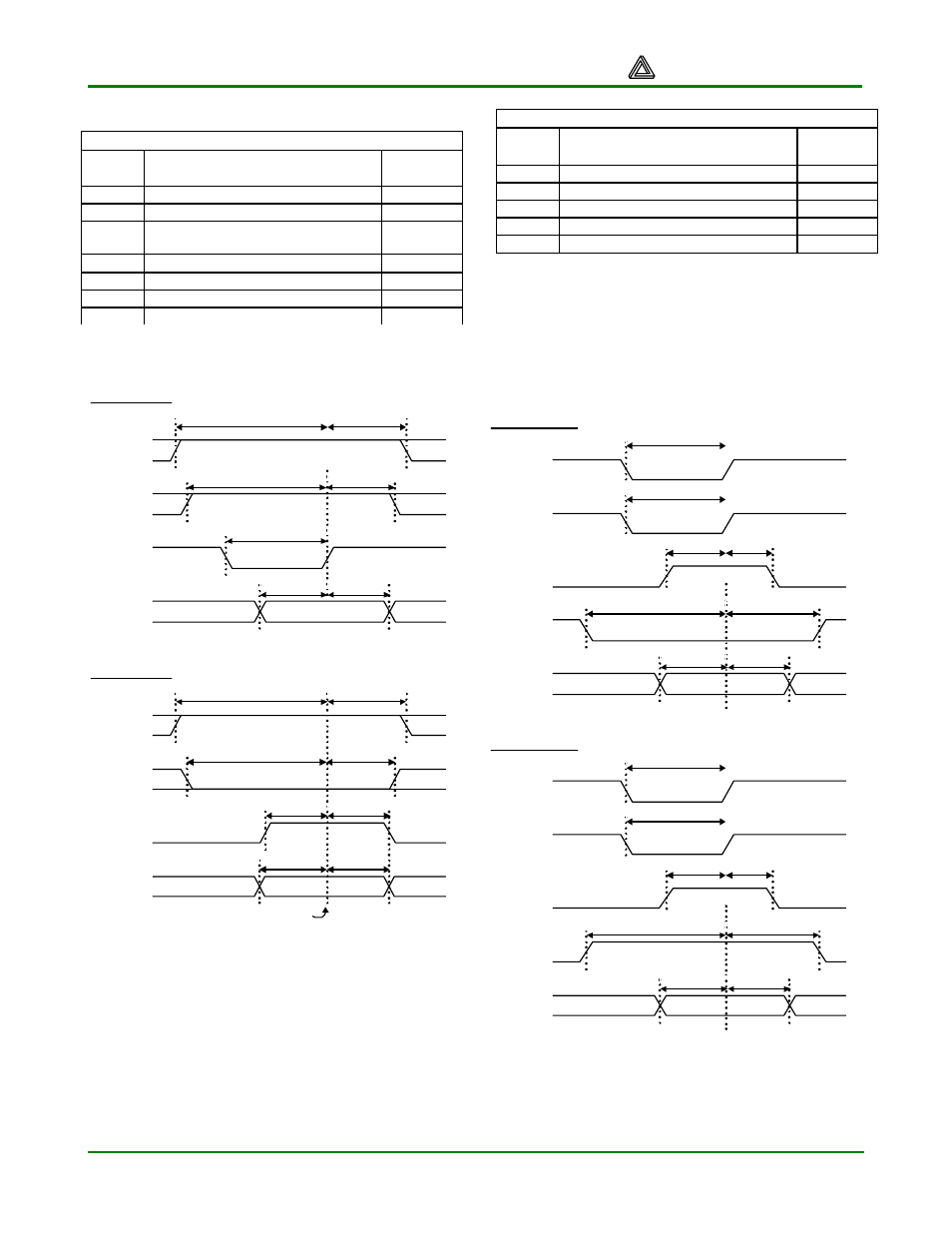

Tw

Th

OE

CS

WE

DB0-DB7

Th

Teoe

Tsu

Tdoe

Ten

Read data latch time

CS

Tdoe

Teoe

OE

WE

Th

DB0-DB7

Tsu

Write Cycle

Read Cycle

Th

Th

Ten

Twd

ASTB

DATA

T

SU

Write Cycle*

Read Cycle*

T

STB

DSTB

WAIT

nWR

T

WT

T

WR

T

STB

* ASTB and DSTB determine whether an address or

data write cycle occurs. Only one should be

asserted for each bus transaction.

Th

ASTB

DATA

Tsu

T

STB

DSTB

WAIT

nWR

T

WT

T

WR

T

STB

T

H

T

H

T

H

T

H

T

H

System Bus Timing

Symb

ol

Parameter

Time

(typ)

ten

Time to enable after CS asserted

10ns

th

Hold time

1ns

tdoe

Time to disable after OE de-

asserted

10ns

teoe

Time to enable after OE asserted

15ns

tw

Write strobe time

10ns

tsu

Data setup time

5ns

twd

Write disable time

0ns

Module Bus Timing

Symb

ol

Parameter

Time

(typ)

tstb

Strobe time

10ns

twt

Strobe to wait time

10 ns

twr

Time to enable write

15 ns

tsu

Data setup time

5 ns

th

Data hold time

5 ns

Figure 14. Peripheral bus signals and timings

- 410-282P-KIT (4 pages)

- 410-279P-KIT (26 pages)

- 410-258P-KIT (16 pages)

- 410-138P-KIT (28 pages)

- 410-178P-KIT (22 pages)

- 410-292P-KIT (29 pages)

- 410-274P-KIT (29 pages)

- 410-182P-KIT (22 pages)

- 410-134P-KIT (17 pages)

- 410-183P-KIT (19 pages)

- 410-155P-KIT (12 pages)

- 6015-410-001P-KIT (26 pages)

- 410-087P-KIT (164 pages)

- 410-146P-KIT (4 pages)

- 6003-410-000P-KIT (138 pages)

- XUPV2P (23 pages)

- 410-047-C2P-KIT (3 pages)

- WaveForms (85 pages)

- 410-297P-KIT (25 pages)

- 410-295P-KIT (37 pages)

- 410-296P-KIT (23 pages)

- 410-209P-KIT REV.D (16 pages)

- 410-209P-KIT REV.C (17 pages)

- 410-254P-KIT (17 pages)

- 410-280P-KIT (9 pages)

- 410-202P-KIT (20 pages)

- 410-273P-KIT (24 pages)

- 410-269P-KIT (11 pages)

- 410-216P-KIT (15 pages)

- 410-231P-KIT (4 pages)

- 410-211P-KIT (10 pages)

- 410-262P-KIT (8 pages)

- 410-229P (7 pages)

- 410-242P-KIT (4 pages)

- 6021-210-000P-KIT (27 pages)

- 410-185P-KIT (21 pages)

- 6032-410-000P-BOARD (4 pages)

- 410-174P (17 pages)

- 410-145P (6 pages)

- 210-264P-BOARD (3 pages)

- 6003-210-012P (27 pages)

- 410-236P-BOARD (2 pages)

- 410-163P (1 page)

- 410-097P-KIT (2 pages)

- 410-255P-KIT (1 page)