Digilent MX4cK User Manual

Page 17

Cerebot MX4cK Reference Manual

www.digilentinc.com

page 17 of 35

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

The standard SPI library supports access to a

single SPI port, SPI2. This is accessed using

the SPI object.

The DSPI library supports access to both SPI

ports. The DSPI0 object class is used to create

an object used to access the default SPI port,

SPI2, connector JB. The DSPI1 object class is

used to access SPI1, connector J1.

I

2

C™ Interface

The Inter-Integrated Circuit (I

2

C

TM

) Interface

provides a medium speed (100K or 400K bps)

synchronous serial communications bus. The

I

2

C interface provides master and slave

operation using either 7 bit or 10 bit device

addressing. Each device is given a unique

address, and the protocol provides the ability

to address packets to a specific device or to

broadcast packets to all devices on the bus.

Refer to the Microchip PIC32MX3XX/4XX

Family Data Sheet and the PIC32 Family

Reference Manual, Section 24, Inter-Integrated

Circuit, for detailed information on configuring

and using the I

2

C interface.

The PIC32MX460 microcontroller provides for

two independent I

2

C interfaces. The Cerebot

MX4cK is designed to provide dedicated

access to one of these interfaces, I2C2, using

I

2

C daisy chain connector J6. The other I

2

C

interface, I2C1, is accessed using I

2

C daisy

chain connector J2. The signals for I2C1 are

shared with Pmod connector JF, and also

appear on pins 1 & 2 of JF.

The I

2

C daisy chain connectors provide two

positions for connecting to the I

2

C signals, SDA

and SCL, as well as power and ground. By

using two-wire or four-wire MTE cables

(available separately from Digilent) a daisy

chain of multiple Cerebot MX4cK boards or

other I

2

C-capable boards or devices can be

created.

The I

2

C bus is an open-collector bus. Devices

on the bus actively drive the signals low. The

high state of the I

2

C signals is achieved by pull-

up resistors when no device is driving the lines

low. One device on the I

2

C bus must provide

the pull-up resistors. On the Cerebot MX4cK,

I2C2 has fixed 2.2K ohm pull-up resistors.

I2C1 has selectable pull-up resistors that can

be enabled or disabled via jumpers J3 and J4,.

The pull-ups are enabled by installing shorting

blocks and are disabled by removing the

shorting blocks. Generally, only one device on

the bus will have the pull-ups enabled.

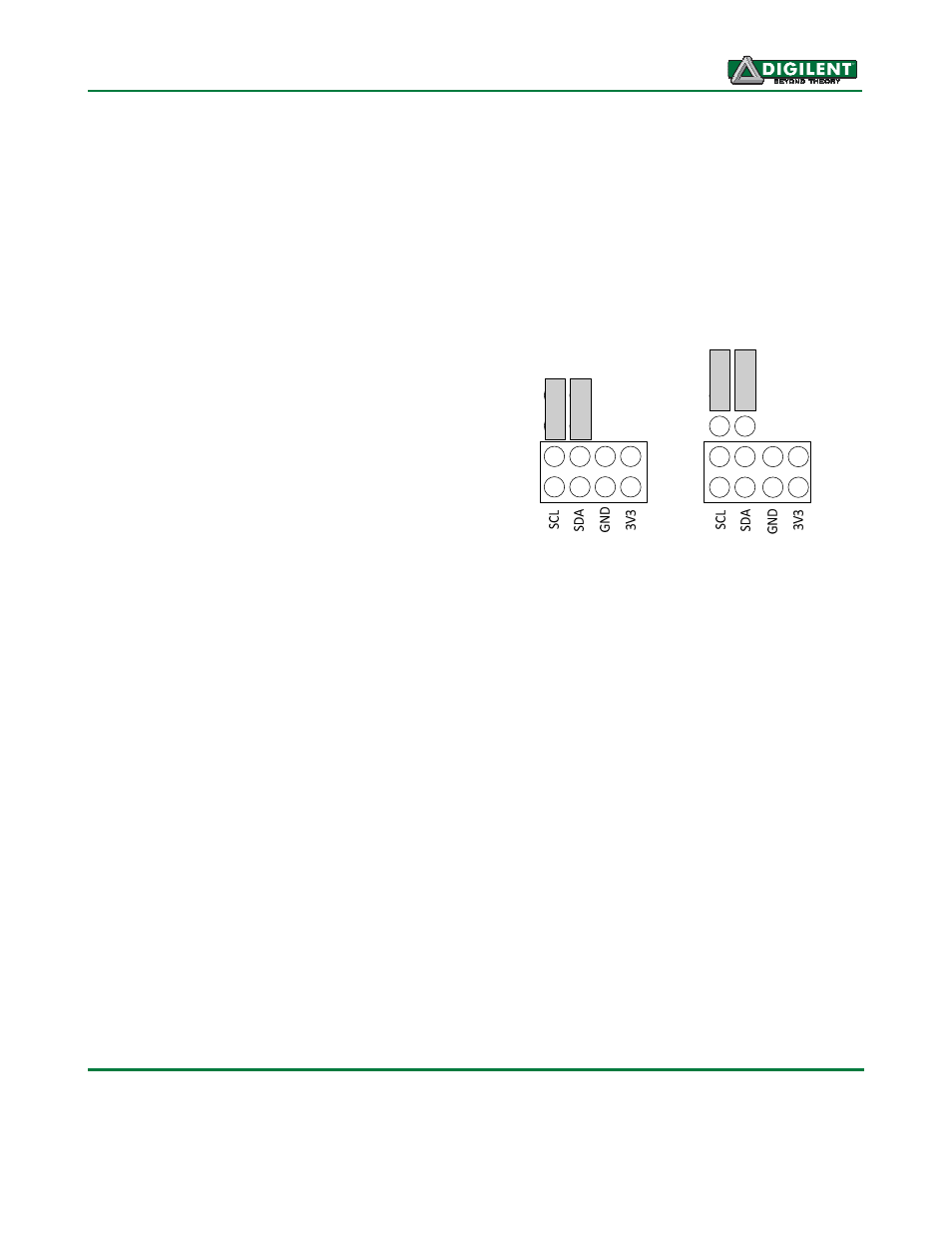

Pull-ups

Enabled

Pull-ups

Disabled

Jumper Settings for I

2

C Pull-Up Resistors

When using the Cerebot MX4cK with the

MPIDE and the chipKIT system, the I

2

C

interfaces are accessed using the standard

chipKIT Wire library, or the Digilent DTWI

library.

The Wire library supports a single I

2

C interface,

I2C1 on J2. This is accessed using the Wire

object.

The DTWI library supports both I

2

C interfaces.

The DTWI0 object class is used to create an

object for access to I2C1 and the DTWI1 object

class is used to access I2C2.

The pinouts of the I

2

C daisy chain connectors

are as follows:

Connector J2. I2C1

• J2-1 – SCL1

• J2-2 – SCL1