Fluke 900 User Manual

Page 55

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

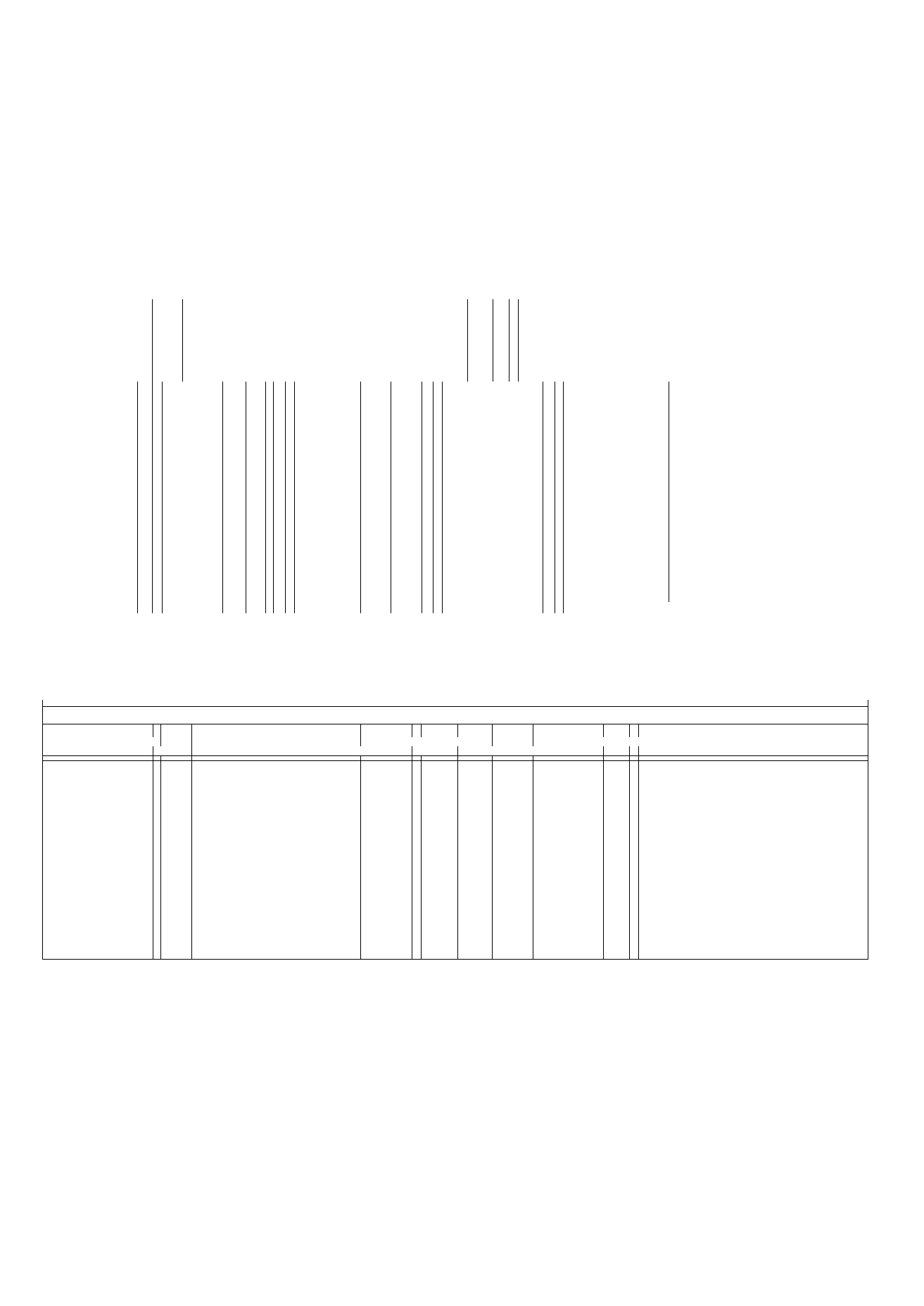

STATE OF MAJOR BLOCKS OF HARDWARE FOR EACH TEST (VER. 5.00 AND LATER)

CONVENTIONS: A-ACTIVE W-WALKING (LINE BY LINE) S-STATIC

P-PULSED(—LO, +-HI) BLANK-NOT APPLICABLE or OFF

f--------------------------------+-------- +---------- +----------+----------+--------------+---------- +------------------------+----------+-----+——+---------- +-------------------+------+--------+--------+------

NAME OF ROUTINE

TEST

#

PULL

-UPS

LATCH

INBUF

SYNC

LATCH

DIFTEST

DRIVERS

HI I LO

------ I-------

SELF

TEST

LATCH

RD

SUPPLY

RELAYS

PIN

DIS

LATCH

FFCLK

LINE

MON

MUX

FREO

CCT.

TRIG

BUFF

TRIGGER

LATCHES

DATAI QUAL

-- +--

ACT

CCT

IMON

BUS

RDBK

SHAD

CCT.

RD

EMUL

CCT.

ADDITIONAL DATA

DGATE

CCT.

SLFT_CLIP

PULLO_MON

PULLl_MON

PULL0_FLT

PULL1_FLT

SYNC0__Hres_FLT

SYNCl_Hres_FLT

SYNCO__Lres_FLT

SYNCl__Lres_FLT

PINDISO FLT

PINDIS1~FLT

SLFTSTO^FLT

SLFTST1_FLT

VccON_FLT

GndON__FLT

PULLPOS_FREQ

TRIGQALO_EQUAL

TRIGQAL1_EQUAL

QAL0__EQUAL

QAL1_EQUAL

TRIGO EQUAL

trigi

“

equal

PULLO TRIG__EQUAL

pulli

”

trig

_

equal

pullo

”

trigqal

FM_STAT NFLT

fm

__

stat

“

flt

FMASK_WB_TEST

FMASK_CAL

FM40_FLT

FM40_NFLT

FM80_FLT

FM80_NFLT

FM120_FLT

FM120_NFLT

FM160_FLT

FM160_NFLT

FM200"

f

LT

FM200_NFLT

FM240_FLT

FM240_NFLT

ACT_DIS_CLR

PULLO_ACT_TSTON

PULLl_ACT_TSTON

PULLO_ACT_ACTSTR

PULL1_ACT_ACTSTR

FREQ_BIAS_SHORT

FREQ_BIAS_LONG

KEYBOARD_OPEN

TEST__CYCLE

UART_TEST

DGATE_TEST

PULL0_XTRIG

PULL1_XTRIG

PULL_XEVENT

SHAD INIT

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

WO

W1

WO

W1

A

A

WO

W1

wo

W1

so

so

so

so

so

S1

W +P

16 1

1

1

1

1

1

1

1

1

1

1

1

1WO 1 wo

17 1

1

1

1

1

1

1

1

1

1

1

1

1W1 1 W1

18 1

1

1

1

1

1

1

1

1

1

1

1

1 SI 1 wo

19 1

1

1

1

1

1

1

1

1

1

1

1

1 so 1 W1

20 1

1

1

1

1

1

1

1

1

1

1

1

1wo 1 SI

21 1

1

1

1

1

1

1

1

1

1

1

1

1W1 1 so

22 1 WO 1

1

1

1

1

1

1

1

1

1

1A

1 SI 1 SI

23 1 W1

1

1

1

1

1

1

1

1

1

1A

1 so 1 SI

24 1 wo 1

1

1

1

1

1

1

1

1

1

1A

1 so 1 SI

50

51

52

53

54

55

56

57

58

59

WO

W1

A

WO/Wl

S1

S1

S1

S1

S1

S1

S1

S1

wo

W1

WVcc

WGnd

S1

S1

S1

S1

S1

S1

WO

W1

S1

S1

S1

S1

25 1

1

1 SI 1 A1A 1SI 1

1 SI 1 SO 1F 1

1

1

1

1

1A

1

1

1

1

26 1

1

1 SO I A1A 1SI 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1

27 1

1

1 SI 1 A1A 1“P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 WIDE-BAND FMASK TESTS

28 1

1

1 SI 1 A1A 1“P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 FMASK

CALIBRATION TEST

29 1

1

1 SI i A1A 1“P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 40ns,

FMASK

< PULSE

30 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 40ns,

FMASK

> PULSE

31 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 80ns,

FMASK

< PULSE

32 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 80ns,

FMASK

> PULSE

33 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 120ns,

FMASK

< PULSE

34 1

1

1 SI I A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

-

120ns,

FMASK

> PULSE

35 1

1

1 SI i A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

-

160ns,

FMASK

< PULSE

36 1

1

1 SI i A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 160ns,

FMASK

> PULSE

37 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 200ns,

FMASK

< PULSE

38 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

-

200ns,

FMASK

> PULSE

39 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 240ns,

FMASK

< PULSE

40 1

1

1 SI 1 A1A 1-P 1

1 SI 1 so 1 F 1

1

1

1

1

1A

1

1

1

1 PULSE

- 240ns,

FMASK

> PULSE

41 1 A 1

1

1

1

1

1

1

I E 1

1

1

1

1 A 1

1

1

1

1 PULSE

ACTCLR!

4 ACTEN 1

42 1

W -PI

A

1

1

1

1

1

1

1 E 1

1

1

1

1A 1

1

1

1

1 ACTIVITY

CCT CONTROLLED

1 BY TESTON

43 1

W +PI

A

1

1

I

1

1

1

1 E 1

1

1

1

1A 1

1

1

1

1 ACTIVITY

CCT CONTROLLED

1 BY TESTON

44 1

W -PI

1

1

1

1

1

1

1 E 1

1

1

1

1A 1

1

1

1

1 ACTIVITY

CCT CONTROLLED

1 BY ACTSTR

45 1

W +P|

1

1

1

1

1

1

1 E 1

1

1

1

1A 1

1

1

1

1 ACTIVITY

CCT CONTROLLED

1 BY ACTSTR

46 1

1

1

1

1

1

1

1

1

1A

1

1

1

1

1

1

1

1

1 FREQ H/W

TESTSHORT

47 1

1

1

1

1

1

1

1

1

1 A

1

1

1

1

1

1

1

1

1 FREQ H/W

TESTLONG

48 1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1 CHECKS THAT ALL KEYS

ARE OPEN

49 1 A 1

A

1 A

1 A1A 1 A 1

A 1

A

1 A

I A 1

i A i A 1 A 1

1

1

1

1

1 INTERRUPTS, TIMERS, TRIGGER, GATE,

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

TEST CLIP LOOPBACK TEST

Vcc RELAYS - PINS 8,9,27,28.1,4.5

Gnd RELAYS - PINS 8-12,14.28,4,7,24,25

SYNC

CHECKS OUT UART/RS232 CIRCUITRY

DGATE - DELAY, DURATION, DIVIDER

EXTENDED TRIGGER - TRIGGER/GATE TEST

EXTENDED TRIGGER - TRIGGER/GATE TEST

EXTENDED TRIGGER - EVENT COUNTER TEST

SHADOW RAM INITIALIZATION TEST

1

E

N

G

I

N E

E R

I N

G

T

E

S

T

S

1

1

PULLI

1

1DIFTEST1 SELF

1RD 1 PIN1

1

1

1 1

TRIGGER

1

IMON1

1 RD1

1

ADDITIONAL DATA

1 NAME OF ROUTINEI TESTI

-UPSI

ISYNC

1 DRIVERS 1 TEST

1 SUPPLY 1

DIS1FFCLK1MON 1FREQ|TRIG|

LATCHES

1ACT 1 BUS

1 SHAD 1EMUL1DGATE|

1 ♦ 1 LATCH 1 :

INBUF1 LATCH 1 HI

1 LO1 LATCH 1 RELAYS 1 LATCH 1 LINE

IMUXICCT.

,1 BUFF 1 DATA1QUAL|CCT|RDBK|CCT.

.ICCT.

.1

CCT. 1

IWALK SIZELEDS

IE601

1

1

1

1 I

1

1

1

1

1

1 1

1

1

1

1

1

1

1 WALK SIZE LED'S ON 4 OFF

ITEST MEMORYIE611

1

1

1

1 I

1

1

1

1

1

i i

1

1

1

1

1

1

1 PARTIAL MEMORY TEST

IWALK MONLEDS

IE62

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 WALK MONITOR LED'S ON 4 OFF

1 UPDATE VCC LIM

IE631

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 UPDATE Vcc MIN AND MAX READINGS

ISHAD ADDR

IE641

1

1

1

1 1

1

1

1

1

1

i 1

1

1

1

i A 1

1

1 SHADOW RAM ADDRESSING TEST (3 min)

1

IE651

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1

1

IE661

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1

1

IE671

1

1

1

1 1

1

1

1

I

1

1 1

1

1

1

1

1

1

1

1

IE681

1

1

1

1 1

1

1

1

1

1

1 i

1

1

1

1

1

1

1

1

IE691

1

1

1

I 1

1

1

I

1

1

1 1

1

1

1

1

1

1

1

IKEY CLOSURE|E701

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 CHECK OF KEY COMBINATIONS

IDISP RAM

IE711

1

1

1

I 1

1

1

1

1

1

i 1

1

1

1

1

1

1

1 DISPLAY RAM TEST/DISPLAY VISUAL TEST

1 RESERVED

1E721

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1

1 RESERVED

IE731

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1

1 DISP__CHAR_SET

IE741

1

1

1

i 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 DUMPS CHAR SET TO DISPLAY

ICART SLFT

IE751

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 CARTRIDGE SELFTEST ** DESTRUCTIVE **

ITEST C ENG IE761 A 1

A

1 A I A1 A 1 A1 A 1

A

1 A 1A 1

i A 1A 1 A 1

!

1

1

1

1 INTERRUPTS, TIMERS, TRIGGER, GATE, SYNCl

lACT^CROSS

IE771 A 1

1

1

1 1

1

1

1

1A 1

i 1

1

1 A 1 1

1

1

1 CROSSTALK TEST - ACTIVITY CIRCUIT

|TRG CROSS

IE781 A 1

1

1

1 1

1

1

1

1

1

1 A 1A 1 A 1

1

1

1

1

1 CROSSTALK TEST - TRIGGER CIRCUIT

IFRQ CROSS

IE791 A 1

1

1

1 1

1

1

1 I A

1 1

1

1

1

1

1

1

1 CROSSTALK TEST - FREQUENCY CIRCUIT

IFLT CROSS

IE801

1

1

1

1 1

1

1

1

1

1

1 1

1

1

1

1

1

1

1 CROSSTALK TEST - FAULT CIRCUIT