Mz3500 – Sharp MZ-3500 User Manual

Page 68

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

MZ3500

6-6. 8253 Controls

Baud rate of this interface will be determined by the clock

output of the 8253. The 8251 is configured such that its

baud rate is 1/16 of the input clock and has the following

relation between the 8253 output clock and the baud rate:

8253 input frequency: 2457.6kHz

8253 Mode set: Mode 3(rec’angle waveform rate generator)

Baud rate

825 3

Output frequency

8 2 5 3

Parameter

1 1 0

,t -

1 7 6 0

h z

1 3 9 6 . 3 6

3 0 0

4 8 0 0

5 I 2

6 0 0

9 6 0 0

2 5 6

I 2 0 0

1 9 2 0 0

1 2 8

2 4 0 0

3 8 4 0 0

6 4

4 8 0 0

7 6 8 0 0

3 2

9 6 0 0

1 5 3 6 0 0

1 6

Control signals

Signal name

Symbol

IN/OUT

Function

Transmission enabled

CS

“* Peripheral

When high, data input from a peripheral is enabled.

When low, data input from a peripheral is disabled.

Data set ready

DR

-♦ Peripheral

Goes high when power is on to the interface unit.

Carrier detect

CD

Peripheral

(SW6-ON) High at all times when power is on to the interface unit.

(SW6-OFF) Goes high only when data is on output.

Beady

READY

Peripheral

Data output from the interface is enabled.

(ON) Data is output from the interface.

(OFF) Waits for data output.

NOTE: A maximum of two bytes are output after the signal goes from high to low

state.

Equipment ready

ER •*- Peripheral

Indicates that the peripheral is ready, it results in an error if low or open when data

is sent from the interface. This signal will be invalidated when the SW5 is turned

off.

Paper out

PO

Peripheral

(SW7-ON) Causes an error if set high during data output.

(SW7-OFF) Causes an error if set low during data output.

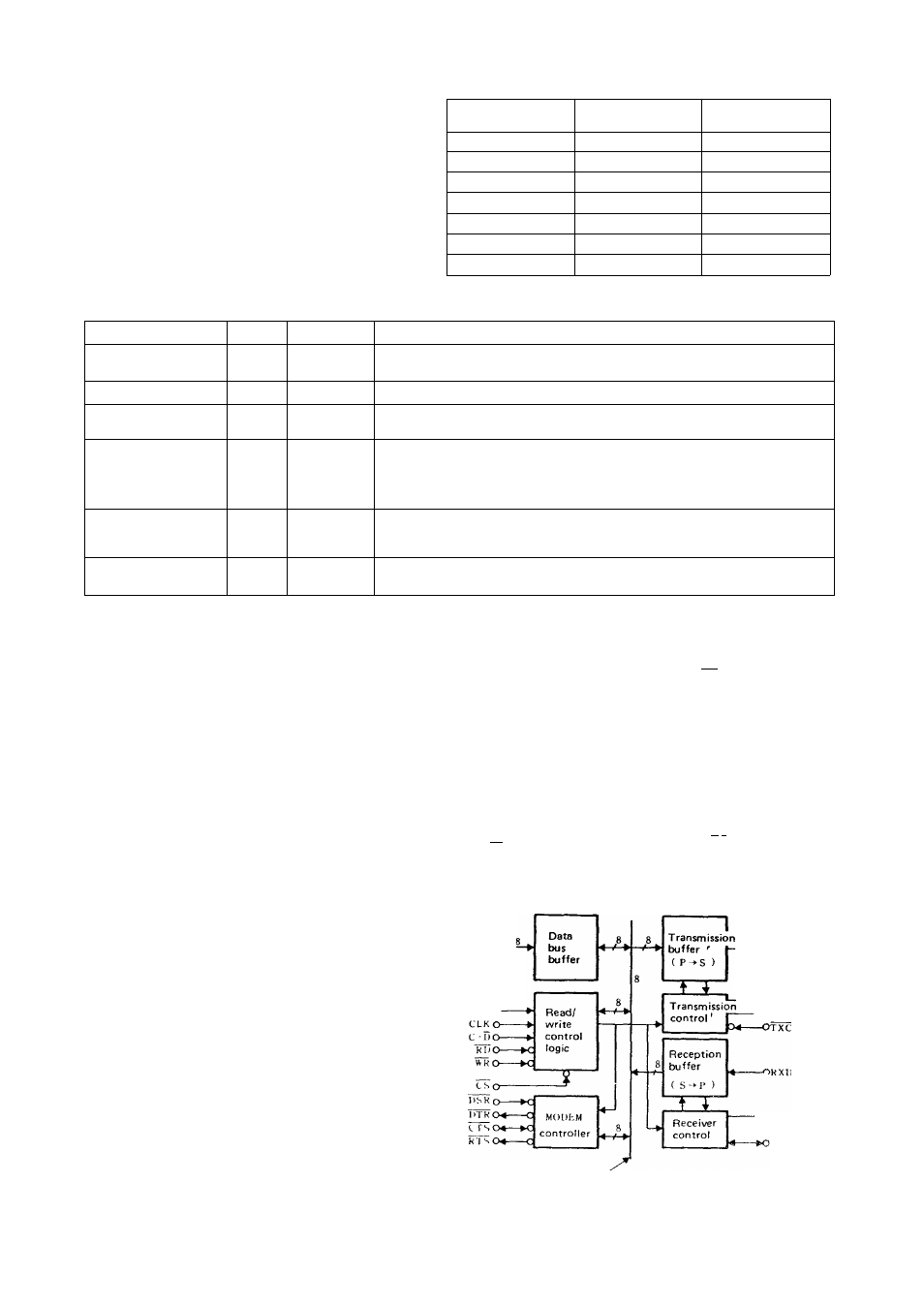

6-7. Description of LSI's

1) UPD8251AC (Programmable Communication Interface)

The UPD8251A is a USART (Universal Synchronous/

Asynchronous Receiver/Transmitter that was specifical

ly designed for data communication.

The USART receives parallel data from the CPU and

converts it into serial data before transmitting. Also,

serial data is received from an external circuit and trans

ferred to the CPU after converting it into parallel. The

CPU can monitor the current state of the USART at

any time (data transfer error, and control signal of

. SYNDET and TXEMPTY.

.-eatures

• 8080A/8085A compatible

• Synchronous/asychronous operation

• Synchronous operation

5 —

8

bits character

Clock rate: baud rate x 1, x16, x64

BREAK character generation

Stop bit; 1, 1.5, 2 bits

Error start bit detection

Automatic break detection and operation.

•

Baud rate: DC — 64K baud

•

Full-duplex

Double buffer type transmitter/receiver

•

Error detect

Parity, overrun, framing

•

Input/output TTL compatible

•

N-channel MOS

•

Single -r5V supply

Single phase TTL level clock

28-pin, plastic DIP

Intel

8251 A

compatible

Pin configuration (Top View)

D2

04

-------- ^

D3 O*-

RXD O—

GND O—

D4 04-

D5

04-

D6 04-

D7 04-

T ) ^ O -

---- 1 0

-I

WHO—

cs o

C -D O

RD O

11

1 2

■►C

15

RXRDY 04

14

D4

.28

,27

26

♦ODl

♦ODD

25

—OVCC

.24

-ORXC

-►ODTR

22

-►O

rts

21

-ODSR

-ORESET

20

■4

^—OCLK

19

18

-►OTXU

-►OTXEMPTY

[04lZ.„-o CTS

,16

15

-►O

SYNDET

BD

-►OTXRDY

Block diagram

D

7

-D

0

C>#-

RESETO

>OTXD

¥CTXK iJ

>

otxe

X)RXRI)/

>4

---- OK^

SYMJhl HI)

Internal data bus

75 -