Mz3500 – Sharp MZ-3500 User Manual

Page 36

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

MZ3500

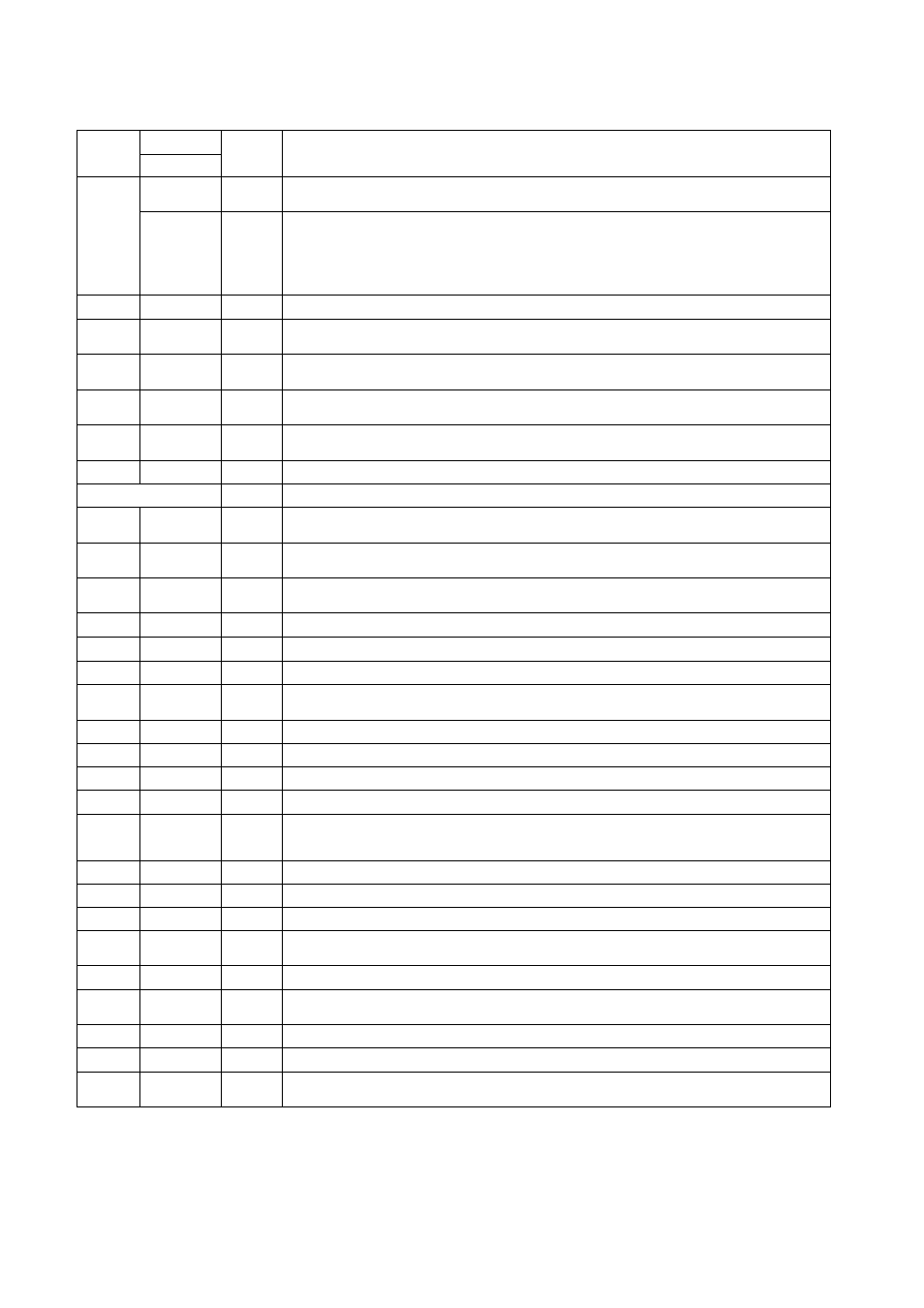

4 6. LSI (CSP 2) SP6012C-003 Signal Description

Pin

No

Polanty

IN/OUT

Function

Signal Name

1

HSY2

IN

Horizontal synchronizing signal from GDC2 which also becomes the refresh tirniny .lynoi in tliC'

dynamic RAM mode.

2

BLK2

IN

Erase signal input from the GDC2 which is supplied 4T the following times:

1. Horizotal flyback period.

2.

Vertical flyback period.

3. Period from the execution of the SYNC SET command to execution of the DtSP START

command.

4. Line drawing period.

3

DWE

OUT

WRITE ENABLE output for the graphic dynamic RAM.

4 ' 5

AD14-AD15

IN

Input of the display output signals {AD14, ADI 5) from GDC2.

(Used to create DBIA-DBIC in the CSP-2.)

6

DBI2

IN

Input from the GDC2 by which the image memory output is sent on the data bus.

(Used to create RASA-RASC, CAS, PS, DWE in the CSP-2.)

7

DBI1

IN

Input from the GDC1 by which the image memory output is sent on the data bus.

(Used to create BUSG, SOE, SWE in the CSP-2.)

8

BUSG

OUT

Gate signal of the bidirection bus buffer (LS245) which is used to read/wnte attribute, and character,

data from the static RAM (2114A-1,6116P-3).

9

SOE

OUT

OUTPUT ENABLE for character static RAM (6116P-3).

10

SWÉ

OUT

WRITE ENABLE for attribute, character static RAM.

1 1

0816

OUT

8-bit/word and 16-bit/word select signal.

(8-bit/word chosen with LDA, ООН OUT#5D, and 16-bit/word is chosen with LDA, 01 H OUTi?5D.)

12

RASI

IN

Memory control siqnal RAS from GDC1.

(Used to create CGOE, SL1 in CSP-2.)

13

RAS2

IN

Memory control signal RAS from CDC3.

(Used to create §L27 LOAD, RASA-RASC, CAS, PS, DBIA-DBIC, DSP2 in CSP-2.)

14

AS3

IN

Address bus input from the sub-CPU (ASS = AB3)

15

NWRO

IN

Chip select (OUT#5X) of the I/O port in CSP-2.

16-17

DS0-DS1

IN

Data bus input from the sub-CPU (DSO = DBO, DS1 = DB1).

18

RA40

IN

The signal that goes to high level (input from CSP-1) when the 400-raster CRT is connected.

(Used for clock frequency selection in CSP-2.)

19

M40

IN

Clock input from the clock generator (39.32MHz, for 400-raster mode.)

20

GND

IN

OV supply

21

SL2

OUT

Graphic ORAM output paraliel/serial converter 1C 74LS166 shift load signal.

22

RASA

OUT

Graphic DRAM (A), (B) RAS signal.

23

2CM2

OUT

Double character clock output. In the character display mode, a single phase clock of the half the

one character wide frequency is supplied. In the graphic display mode, a single phase clock of

8/16 dot frequency is supplied to GDC2.

24

LOAD

OUT

Graphic DRAM output paraliel/serial converter 1C 74LS166 load timing clock.

25

Vcc

IN

+5V supply.

26

FYD2

OUT

Graphic DRAM output paraliel/serial converter 1C 74LS166 shift out clock.

27

2CK1

OUT

Double character clock output same as 2CK2. In the character display mode, a single phase clock

of one half the one character wide frequency is supplied to GDC1.

28

SL1

OUT

Character CG output paraliel/serial con>^rter 1C 74LS166 shift out clock.

29

SL1

OUT

Character CG output paraliel/serial converter 1C LS166 shift load signal.

Character CG address.

30

CGOE

OUT

Character CG output enable signal.

31-33

DB1C-DB1A

OUT

Timing signal by which the graphic DRAM output is sent on the data bus.

34-35

RAS-C -

RAS-B

OUT

Graphic DRAM RAS (ROW ADDRESS SELECT) siqnal.

RAS-B; RAM(C), (D) RAS-C; RAM (E), (F)

- 41 -