5. memory (romipl, ramcom, s ram) select circuit, Mz3500 – Sharp MZ-3500 User Manual

Page 21

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

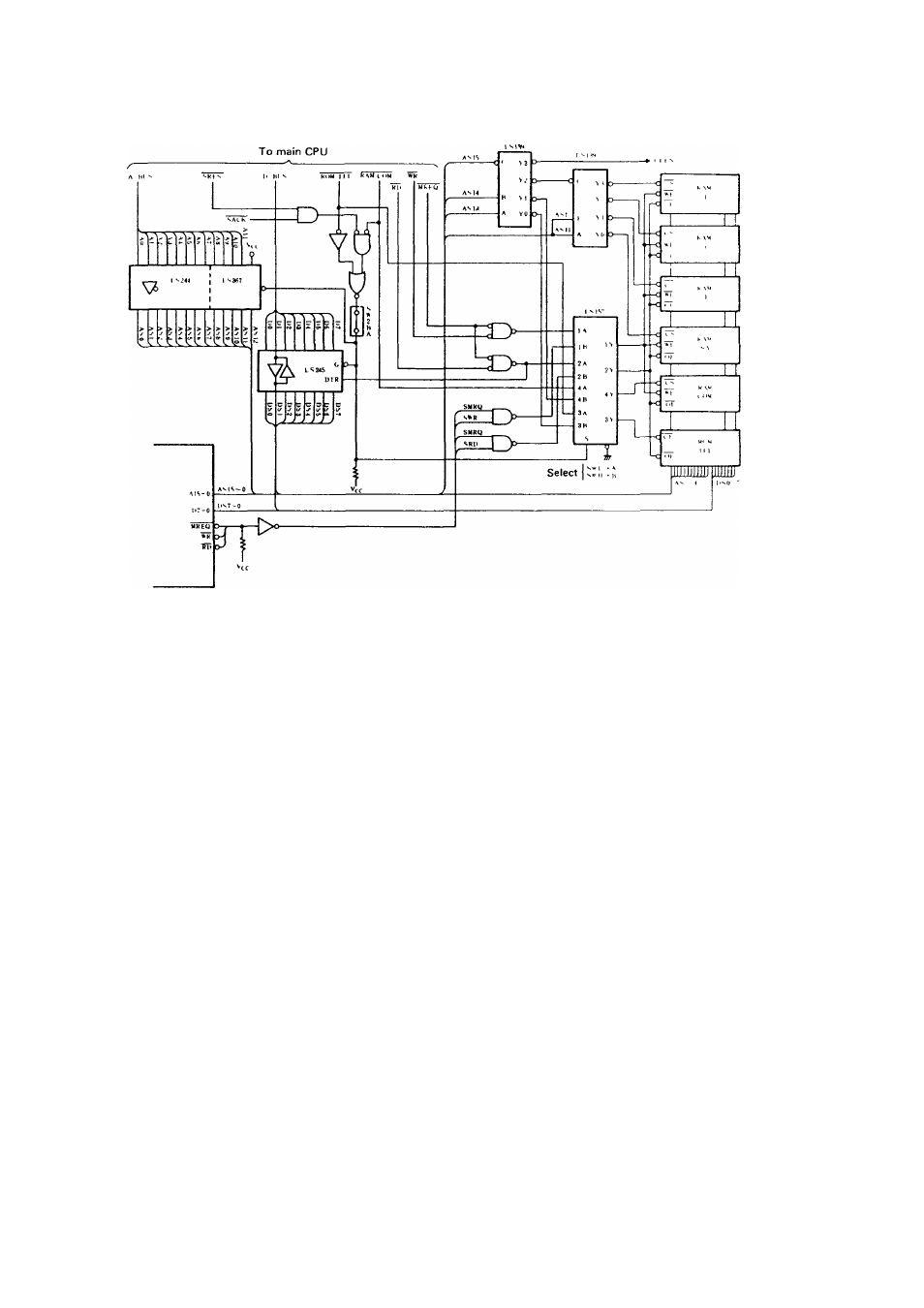

3-5. Memory (ROMIPL, RAMCOM, S RAM) select circuit

MZ3500

1) ROM-IPL select by the main CPU

As ROM IPL turns to low level after power on address

bus

buffers

{LS244,

LS367)

and

data

bus

buffer

(LS245) are enabled. S of the data selector 1C (LS157)

is set to a low level to enable input 1A-4A. The 3Y and

2Y outputs of the LSI 57 then go low so that CE and OE

of the ROM-IPL are from main CPU. The contents of

the IPL-ROM are then read by the main CPU. Because

the input pin (ff16) of the address buffer (LS367) is

connected to Vcc, IPL for the main CPU will be at

address

1000

of

the IPL-ROM. Switch

SW2BA is the

operation test dip switch which should be ON at all

times.

2) RAM-COM select by the main CPU

When RAM COM is low, SRES high, and SACK low, the

select input S of the selector 1C (LSI 57) is in low state

so that input 1A-4A becomes effective. That is, the out

put 4Y is low and either 1Y (WE) or 2Y (OE) becomes

low level, so as to enable to read or write RAM-COM.

3) ROM-IPL select by sub-CPU

Normally, the select signal S of the selector is pulled up

to Vcc level that inputs 1B-4B are enabled by sub CPU.

If A13 thru A15 were to be at low level, the output YO

of the LSI39 becomes low level so that the output 3Y

of the LS147 or CE of the ROM-IPL should be at low

level. Should SRD, SMRO be at low lebel as well, the

output 2Y of the LSI57 or OE of the ROM-IPL turnde

to low lebel to read the ROM-IPL. Though the sub-CPU

can access an address range of 0000 to 1FFF theoretical

ly, it would be from 0000 to OFFF, actually.

4) RAM-COM select by sub-CPU

Y1 of the LS139 changes to low level when AS13 is high

and AS14 and AS15 are low. In other words, the input

4B of the LSI 57 is at low level which brings the output

Y4 to low level, so that CS of the RAM-COM chip select

signal should become effective.

If SMRO, SRD or SMRO, SWR is in low level at this

point, it enables read (OE) or write (WE). Address range,

however, is 2000 to 3FFF

5) RAM (SA, SB, SC, SD) select by sub-CPU

SMRO, S^ (OE) or SMRO, SWR (WE) is at low level

to

select

the

sub-CPU

dedicated

RAM,

SA-SD.

Tne

following

chip

select

signal,

then

becomes

valid

under

these conditions:

RAMSA .. AS11, AS12, AS13, AS14, AS15

(address 4000-47FF)

RAMSB .. AS11, AST2, ASi^, AS14, AS15

(address 4800-fFFF)

RAMSC .. AS11, AS12, AS13, AS14, AS15

(address 5000-57FF)

RAMSD .. ASH, AS12, AST3, ASK, AS15

(address 5800-5FFF)

- 24 -