M7-3s00 – Sharp MZ-3500 User Manual

Page 18

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

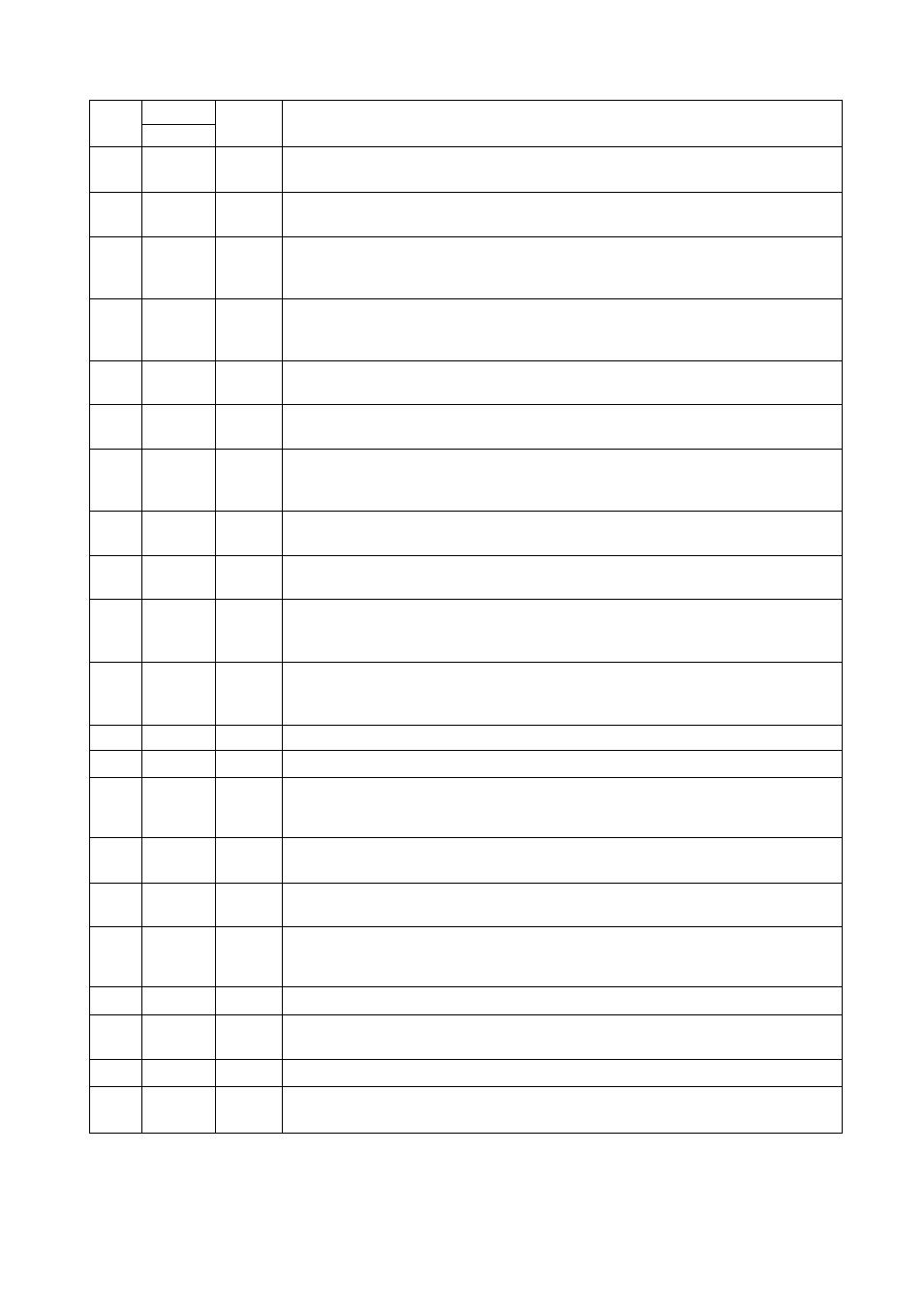

M7-3S00

Pin No.

Polarity

IN/OUT

Function

Signai Name

32

RF1B

OUT

Mam CPU 128KB dynamic RAM output buffer (LS244) output enable signal.

(RAM buffer 1)

33

RF2B

OUT

Signal identical to R F1 B For option RAM

(RAM buffer

2

)

34

WATB

OUT

Wait signal to the mam CPU

(One wait cycle is applied during the memory fetch cycle of the main CPU. It consists of one dock

period) (WAIT)

35

RCMB

OUT

Chip select signat issued from the main CPU to select the RAM shared by the main CPU and

the sub-CPU

(RAM Common)

36

ITFB

IN

Interrupt input from the UPD765 FDC (Floppy Disk Controller). |

(Interrupt from Floppy)

37

ITOB

IN

Interrupt input from the sub-CPU.

(Interrupt from No. 0)

38

39

IT1B

ÏT2B

IN

Interrupt input from slot 1 or 2.

(Interrupt from No. 1, 2)

40

MRQB

IN

Memory request signal from the main CPU.

(Memory Request)

41

IN

Write signal from the mam CPU.

(Write)

42

43

IT3B

ÏT«

IN

Interrupt input from slot 3 or 4.

(Interrupt from No. 3, 4)

44

SEC

IN

Input from the FDD (Floppy Disk Drive) assignment dip switch (A), No. 1.

*See the dip switch description, provided separately.

(Section)

45

GND

IN

Ground

46

Vcc

IN

5V supply

47

48

SW1

SW2

IN

Input from the svstem assignment dip switch.

*See The dip swtch description, provided separately.

49

AO

IN

Mam CPU address bus

Used in the I/O port select logic in the MMR to designate device number.

50

RFSH

IN

Refresh signal from the main CPU,

(Refresh)

61

52

SW3

SW4

IN

Input from the system assignment dip switch.

'See the dip switch description, provided separately.

53

GND

IN

Ground

54

FD1

IN

Input from the system assignment dip switch.

'See the dip switch description, provided separately.

55

Vcc

IN

5V supply.

56

FD2

IN

Input from the FDD assignment dip switch (A), No. 2.

'See the dip swi*ch description, provided separately.

- 21 -