Mz3500 – Sharp MZ-3500 User Manual

Page 38

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

MZ3500

4-7. GDC (Graphic display controller) (UPD7220) signal description

Pin No.

Polarity

Signal Name

2XCCLK

DBIN

HSYNC-REF

IN/OUT

IN

OUT

OUT

Function

Double character cloci< supplied from the external dot timing generator which has the following

two modes:

1. Character display mode' Single phaseclock at one half of the one character wide cycle

2. G'^aphic display mode: Single phase clock of eight dots that cycles

Memory contrc signal supphed to the image memory from the GDC. which causes the image

memory output data to be sent on the data bus.

Memory contro' signal sent to the image memory from the GDC, which is the horizontal

synchronizing signal.

♦ Since the image drawing process is automatically interrupted m the dynamic RAM mode the refresh

address is output during the HSYNC period. It can also be used as the refresh timing signal.

• Refresh is accomplished by suppressing the CAS signal derived from the RAS signal in the external

circuit when the HSYC is at high lebel (Horizontal Synchronous — Refresh timing)

VSYNC

EX.SY

NC

IN/OUT

Establishes one of following two modes, depending on whether the GDC is operated by the master

or the slave.

1. When the master is operational: sends out the vertical synchronizing signal.

2. When the slave is operational: The synchronizing signal generation counter is initialized by a high

level input.

BLNK

OUT

Erase signal output is issued at the following times (blanking signall:

1. Horizontal flyback period.

2. Vertical flyback period

3. Period from the execution of the SYNC SET command to the execution of the DISP START

command.

RAS

OUT

Memory control signal sent to the image memory from the GDC,__________________

• In the dynamic RAM mode, it is used as the reference signal of RAS. When at high level, used

as the timing signal by which the address signal is latched.

(Row Address Strobe)

DRQ

(NO USE)

OUT

DMA request output which is connected with the DRQ input of the DMA controller is output by the

following two commands'

1. DREQE (DMA request write): CPU memory to image memory.

2. DREQR (DMA request read). Image memory to CPU memory.

It will be continuously output until the DMA transfer word/byte number set by the VECTW (vector

write) command becomes zero.

(DMA Request)

DACK

(NO USE)

IN

Signal supplied from the DMA controller that is subsequently decoded by the GDC as the read or

write signal during DMA.

(DMA Acknowledge)

10

RD

IN

In the external circuit RD is combined with the chip select signal (CS). And is used when the CPU

reads from the GDC either data or status flag and the signal DACK.

(Read strobe)

WR

IN

In the external circuit WR is combined with the chip select signal. And is used when the CPU

writes to the GDC either a command or parameter and the signal DACK.

(Write strobe)

1 1

AO

IN

Normally, connected with the address line and is used

to

designate data type.

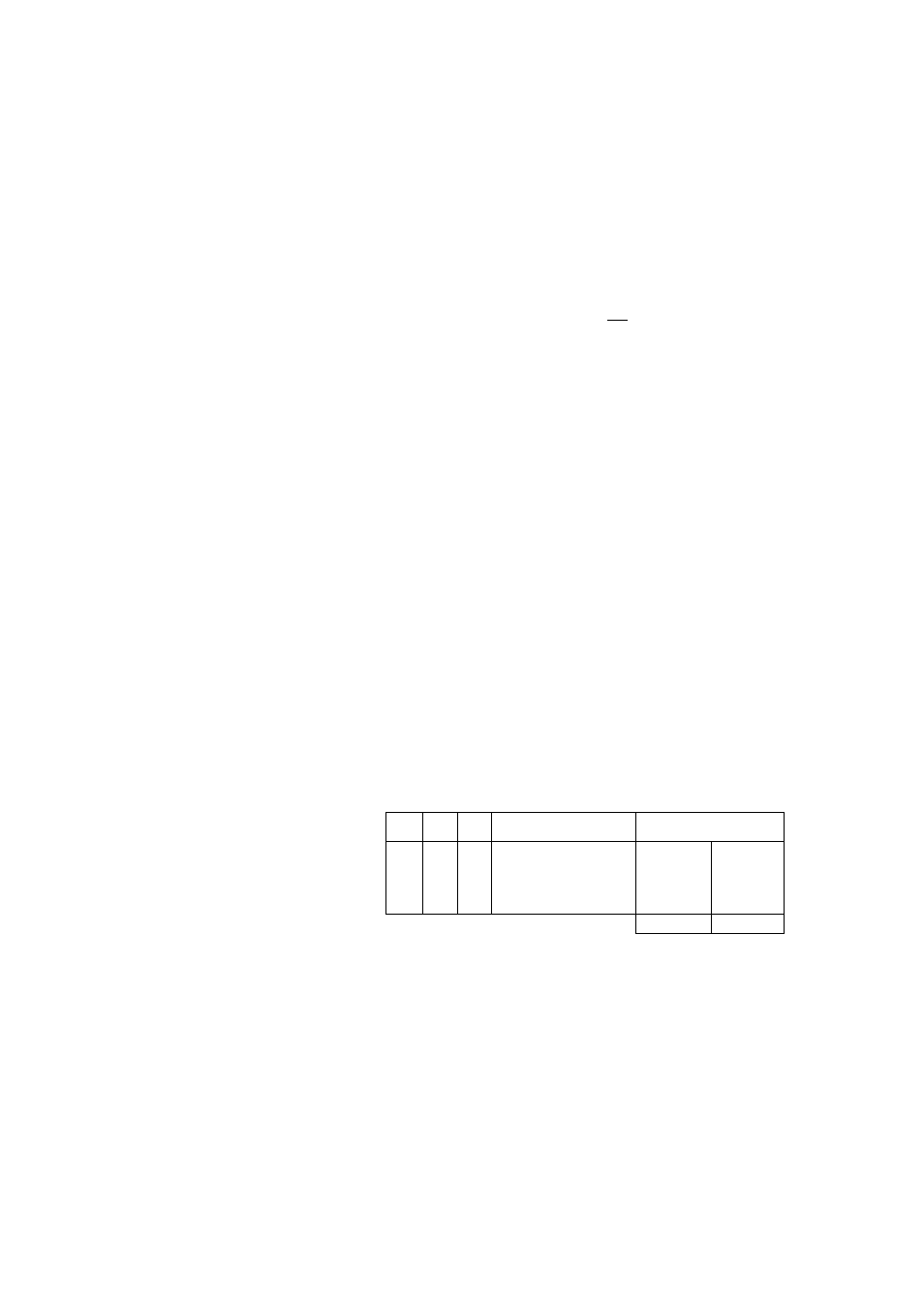

AO

RD

WR

Function

Device number of

the Model 3500

0

0

1

READ STATUS FLAG

IN

#70

IN #60

1

0

READ DATA

IN

#71

IN #61

0

1

0

WRITE PARAMETER

OUT

#70

OUT #60

1

1

0

WRITE COMMAND

OUT

#71

OUT #61

GDC1

GDC2

(Address Bus 0)

12-19

D80-DB7

IN/OUT

Bidirectional data bus connected to the system bus.

(Data Bus 0-^7)

20

GND

IN

OV supply.

21

22-34

LPEN

IN

Light pen strobe input. When a input light is sensed by the light pen, it outputs a high level signal.

The CPU can then read the display address via the LPENR (Light Pen Read) command.

AD0-AD12

IN/OUT

Bidirectional address/data bus connected between the image memory and the GDC on which address

and data are sent on the bus by means of multiplexer ALE (Address Latch Enable) is drived from

the RAS output m the exte'-nal circuit.

(Address/Oata bus 0 •'- 1 2)

- Id