Sd2 (rom based basic) – Sharp MZ-3500 User Manual

Page 11

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

MZ3500

Operational description

(

1

)

As soon as the sub-CPU is started, it initializes the I/O

port and waits for program transfer (IOCS) from the

main CPU. This IOCS (Input Output Control System)

is the program resident at address 4000H-5FFFH.

(2) As the main CPU loads the information from sector

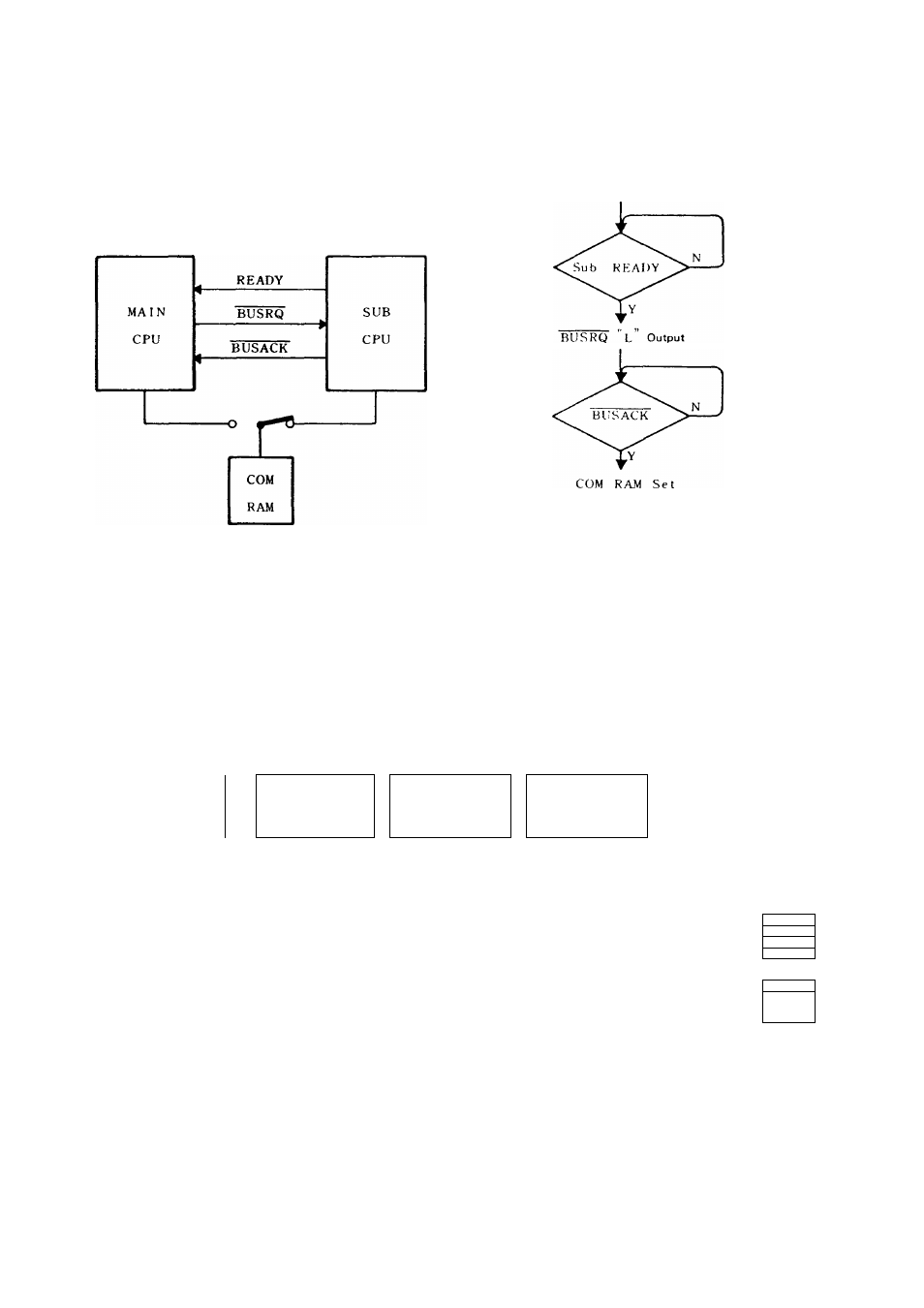

Communication between Main and SUB CPU

"1" of track "0" of the floppy disk, it loads the IOCS

and bootstrap routine to the sub-CPU.

(3) The bootstrap program is loaded next.

(4) The bootstrap program determines memory allocation.

I

"

h

I

BUSRQ H OUTPUT

(ISOLATION OF COM RAM)

2.3. SD2 (ROM based BASIC)

SD2 is active when "SHARP BASIC" is executed via ROM.

RAM

BANK

SELECT

MA3 0 0

MA2 0 0

MAI 0 0

MAO 0 1

FFFF

c o o o

BFFF

4000

I

fff

2 0 0 0

I FFF

0000

K A M A

4

1

KOMB

M02 0

MO] 0

MOO 0

MAIN CPU

ROM 2 ROMS

MSI = u H )

Mso = 0 L;

—I—1—1—

KAMb

---------1--------1--------

\

--------

К AM L

-------- 1--------1--------1-------

K A M I *

1, 2 1 3|

A

1

1

2

,

3 , 4

______i | г , 3 | 4

\

\ \

\ \

\\

\ \

\\

SUB CPU

\\

\ \

\ \

\ \

\\

RAM SD

RAM

s c

RAM SB

RAM SA

RAM(aX)

ROM J PL

1. Bank select. MA0~MA3, is effective for memory area COOOH-FFFFH.

2. Bank select. MOO—MA2, is effective for memory area 2000H-3FFFH

10 -