M z 3500 – Sharp MZ-3500 User Manual

Page 34

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

M Z 3500

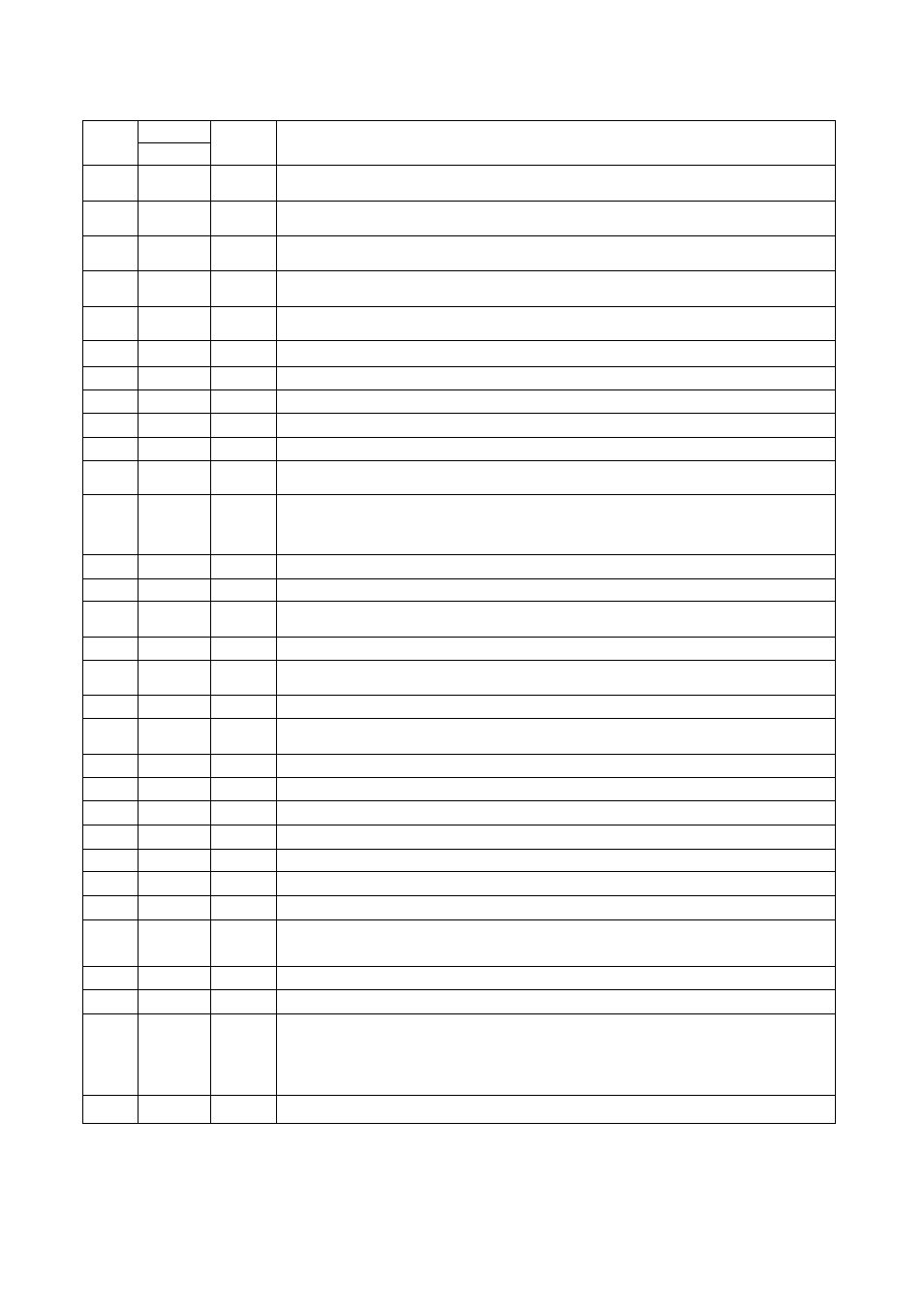

4Æ. Master slice LSI (CSP-1) SP6102C 002 signal description

Pm No.

Prionly

IN/OUT

Function

Signal Name

1

HSY.

IN

Horizontal synchronizing signal from the GDCl Also, it becomes the refresh timing signal in the

dynamic RAM mode.

2

NABC

IN

Input from the UPO7220 GOC1. When the GDCl is in the character display mode, the attribute,

blinking timing and line counter clear signals are multiplexed.

3

CSR

IN

Input from the GDC1 which is the cursor display input when the GDCl is in the character display

mode.

4 ~ 6

ASO - AS2

IN

Address bus input from the sub-CPU.

ABO = ASO, ABl = AS1, AB2 = AS2

7 ~ 9

DSO - DS2

IN

Data bus input from the sub-CPU.

DBO = DBO. DB1 = DB1, DB2 = DB2

10

G2

OUT

Green image output to the CRT2.

11

NWRO

IN

CSP1 I/O port select signal (OUT #5X)

12

"Nve

IN

Input of The blue image from the graphic RAM(A) and (B).

13

NVR

IN

Input of the red image from the graphic RAM (B), (C), and (D).

14

NVB

IN

Input of the green image from the graphic RAM (E) and (F).

15

FYD2

IN

Input of the graphic RAM parallet/senal conversion 1C 74LS166 shift out clock.

(Used to latch the image data in CSPI.)

16-18

AT2 - AT4

IN

Attribute data input from the 2114A-1 attribute RAM.

fAT-2 — Horizontal tme/R ')

AT-3 ~ Reverse/G 1

[

a

T-4- Blink J

19

CH

IN

Input of character display data signal.

20. 21

GND

IN

OV supply

22

DSP2

IN

Input of display timing signal supplied from the CSP-2. (BLINK signal from the GDC2 is delayed by

two flipflop intervals in the CSP-2 to créât this signal.)

23

VID2

OUT

VIDEO output to CRT2.

24

LCO

OUT

Character CG line counter output.

(Becomes address input to the CG when LCO = CG address AO.)

25

ATI

IN

Attribute data input (vertical Ilne/B) from the 2114A-1 attribute RAM.

26-28

LC1 - LC3

OUT

Character CG line counter output.

(LC1 = A1, LC2 = A2, LC3 = A3CG = A3)

29

NCL4

OUT

Character CG output data latch timing.

30

HSYO

OUT

CRT1,2 horizontal synchronizing signal

31

RA40

OUT

The signal that turns high level when the 400-raster CRT is m connection. LDA, 01 H OUT??56

32

VIDI

OUT

VIDEO output to the CRT1.

33

81

OUT

Blue image output to the CRT1.

34

R1

OUT

Red image output to the CRT1.

35

g

T

OUT

Green image output to the CRTl.

36

SL1

IN

Character CG output parallel/serial converter IC 74LS166 shift load signal, and character CG address

latch signal input. (Used for the image data latch signal in the CSP-1 and horizontal synchronizing

signal delay flipflop clock.)

37

82

OUT

Blue image output to CRT2. ■

38

R2

OUT

Red image output to CRT2.

39

BLNK

IN

Erase signal from the GDC1 which becomes input at the following times.

1. Horizontal flyback period

2. Vertical flyback period

3. Period from the execution of the SYNC SET command to the execution of the DISP START

command.

4. Line drawing period

40

Vcc

IN

+5V supply.

39