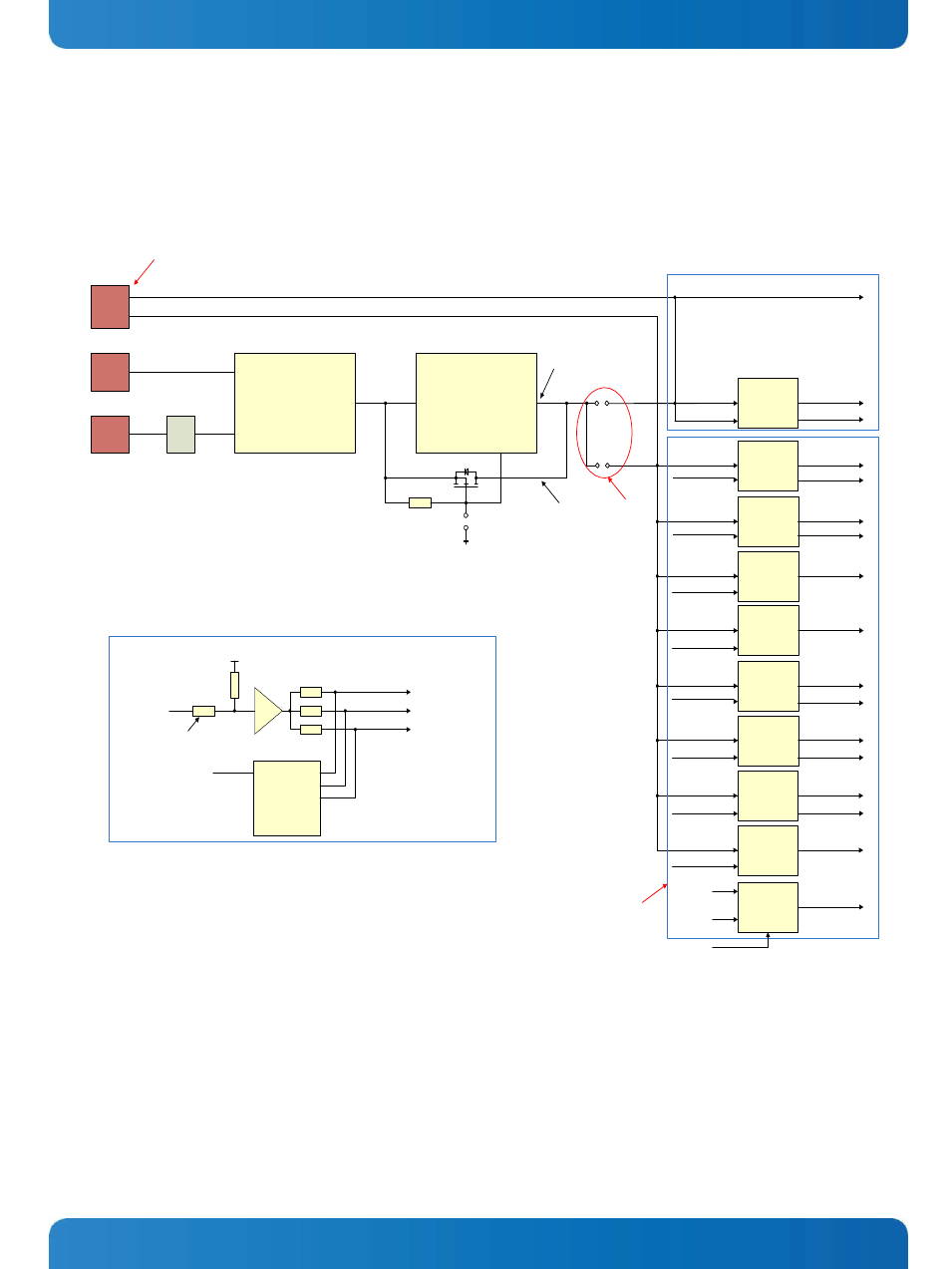

2 figure 17 power architecture, Figure 17. power architecture, Figure 17 power architecture – Kontron SMARC Evaluation Carrier User Manual

Page 66

User’s Guide

66

IN MAX1818 OUT

SHDN#

POK

V_1V8_LDO

1V8_LDO_POK

IN TPS63020 OUT

EN

PG

V_5V0_USB @2A

PG_5V0_USB

17.2 Figure 17 Power Architecture

J29

BENCH

SUPPLY

CONNECTOR

IF CHARGER POWER

AND / OR BATTERY

POWER ARE USED,

THEN BENCH SUPPLY

INPUT MUST BE LEFT

OPEN

3.0V TO 5.25V MODULE POWER

3.0V TO 5.25V CARRIER POWER

MODULE POWER DOMAIN

MODULE POWER

J28

CHARGER

CONNECTOR

J23, J24, J25

BATTERY

CONNECTORS

V_CHARGER

BATTERY

SELECT

JUMPERS

V_BAT

IN

IN / OUT

BATTERY CHARGER

CIRCUITS

OUT

STEP-DOWN SWITCHER

WIDE INPUT RANGE

NOT USED FOR SINGLE LEVEL CELLS

IN

IS USED FOR TWO AND THREE LEVEL

SERIES CELLS

ENABLE

P-FET

OUT

5V OUTPUT IF

SWITCHER IS USED

J56

J55

MODULE POWER

1V8_LDO_SHDN#

CARRIER POWER

V_5V0_USB_EN

BATTERY

V_CHARGER

V_BAT

V_BAT

CONFIG

NOMINAL RANGE

SINGLE LEVEL

~ 5V

3.6V

3.0V - 4.2V

TWO SERIES

~10V

7.2V

6.0V – 8.4V

Resistor

J27

Switcher Bypass Jumper

3.0V – 5.25V IF

SWITCHER IS

BYPASSED

JUMPERS J56 AND J55

MUST BE OPEN WHEN

POWER IS BROUGHT IN

IN TPS63020

OUT

V_5V0 @2A

THREE SERIES

~15V

10.8V

9.0V – 12.6V

(SINGLE LEVEL CELL)

FROM BENCH SUPPLY

CONNECTOR J29

V_5V0_EN

EN

PG PG_5V0

IN LP8545

OUT

V_31V9 @300mA

LCD_BKLT_EN

EN

CARRIER POWER ENABLE SCHEME – IN MODULE POWER DOMAIN

IN TPS61087 OUT

V_1V8_LDO

V_12V_EN

EN

CARRIER_PWR_ON

MODULE PIN S154

R275

POWER ENABLES

(ONLY 3 OF MANY SHOWN)

IN

V_1V5_EN

EN

TPS53310

OUT

PGD

V_1V5 @3A

PG_1V5

MAY BE NOT

INSTALLED

IN TPS63020 OUT

V_3V3 @2A

V_3V3_EN

EN

PG PG_3V3

I2C_PM

I2C I/O Expander

I/O pins default to being inputs

V_3V3_PCIE_EN

IN TPS63020

EN

OUT

PG

V_3V3_PCIe @2A

PG_3V3_PCIE

IN TPS62020

OUT

V_1V8_EN

EN

CARRIER POWER DOMAIN

V_3V3

V_1V8

V_IO Select

PFET Power Switches

Low:1V8

V_IO

SMARC VDD_IO_SEL#

Figure 17. Power Architecture