6 parallel ata harddisk interface, 986lcd-m family – Kontron 986LCD-M-mITX (BGA) User Manual

Page 36

986LCD-M Family

KTD-N0837-B

Public

User Manual

Date: 2012-04-17

Page

36 of 91

4.6 Parallel ATA harddisk interface

One parallel primary ATA harddisk controller is available on the board.

Standard 3½” harddisks or CD-ROM drives may be attached to the primary controller board by means of the

40 pin IDC connectors, IDE_P.

The primary controller is shared between the IDE_P connector and the backside Compact Flash connector

(986LCD-M/mITX only). In case CF is utilized, only one IDE device is supported on the IDE_P connector.

The harddisk controllers support Bus master IDE, ultra DMA 33/66/100 MHz and standard operation modes.

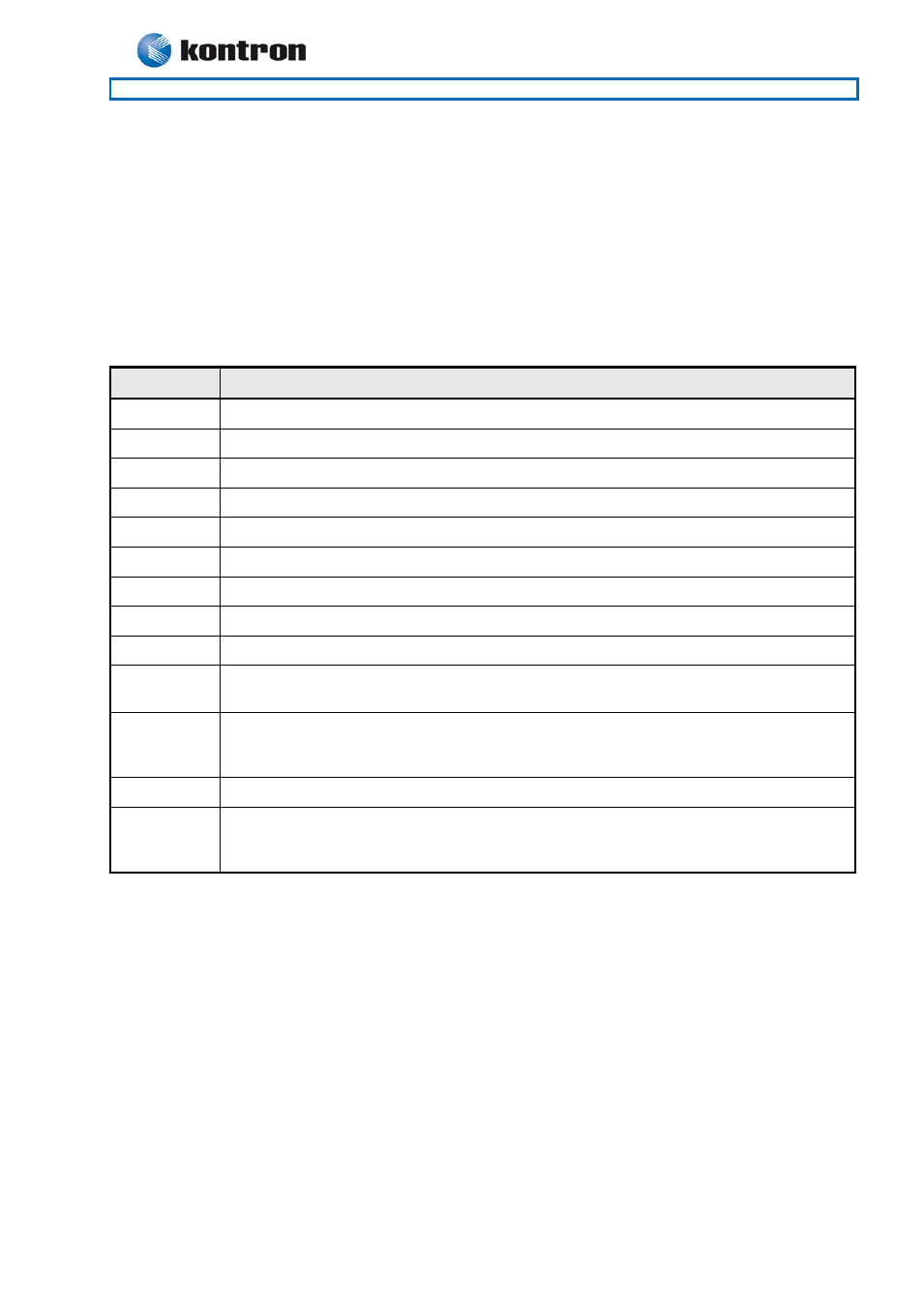

The signals used for the harddisk interface are the following:

Signal

Description

PDA2..0

Address lines, used to address the I/O registers in the IDE hard disk.

HDCS1..0#

Hard Disk Chip-Select. HDCS0# selects the primary hard disk.

D15..8

High part of data bus.

D7..0

Low part of data bus.

IOR#

I/O Read.

IOW#

I/O Write.

IORDY#

This signal may be driven by the hard disk to extend the current I/O cycle.

RESET#

Reset signal to the hard disk. The signal is similar to RSTDRV in the PC-AT bus.

HDIRQ

Interrupt line from hard disk. Routed by the SiS630 chipset to PC-AT bus interrupt.

CBLID

This input signal (CaBLe ID) is used to detect the type of attached cable: 80-wire cable

when low input and 40-wire cable when 5V via 10Kohm (pull-up resistor).

DDREQ

Disk DMA Request might be driven by the IDE hard disk to request bus master access to

the PCI bus. The signal is used in conjunction with the PCI bus master IDE function and is

not associated with any PC-AT bus compatible DMA channel.

DDACK#

Disk DMA Acknowledge. Active low signal grants IDE bus master access to the PCI bus.

HDACT#

Signal from hard disk indicating hard disk activity. The signal level depends on the hard

disk type, normally active low. The signals from primary and secondary controller are

routed together through diodes and passed to the connector FEATURE.

All of the above signals are compliant to [4].

The pinout of the connectors are defined in the following sections.