Cirrus Logic EP7312 User Manual

Page 34

34

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS508F2

EP7312

High-Performance, Low-Power System on Chip

79

SMPCLK

1

Low

O

SSI1 ADC sample clock

80

FB[1]

I

PWM feedback input

81

VSSIO

Pad Gnd

I/O ground

82

FB[0]

I

PWM feedback input

83

COL[7]

1

High

O

Keyboard scanner column

drive

84

COL[6]

1

High

O

Keyboard scanner column

drive

85

COL[5]

1

High

O

Keyboard scanner column

drive

86

COL[4]

1

High

O

Keyboard scanner column

drive

87

COL[3]

1

High

O

Keyboard scanner column

drive

88

COL[2]

1

High

O

Keyboard scanner column

drive

89

VDDIO

Pad Pwr

Digital I/O power, 3.3 V

90

TCLK

I

JTAG clock

91

COL[1]

1

High

O

Keyboard scanner column

drive

92

COL[0]

1

High

O

Keyboard scanner column

drive

93

BUZ

1

Low

O

Buzzer drive output

94

D[31]

1

Low

I/O

Data I/O

95

D[30]

1

Low

I/O

Data I/O

96

D[29]

1

Low

I/O

Data I/O

97

D[28]

1

Low

I/O

Data I/O

98

VSSIO

Pad Gnd

I/O ground

99

A[27]/DRA[0]

2

Low

O

System byte address /

SDRAM address

100

D[27]

1

Low

I/O

Data I/O

101

A[26]/DRA[1]

2

Low

O

System byte address /

SDRAM address

102

D[26]

1

Low

I/O

Data I/O

103

A[25]/DRA[2]

2

Low

O

System byte address /

SDRAM address

104

D[25]

1

Low

I/O

Data I/O

105

HALFWORD

1

Low

O

Halfword access select output

106

A[24]/DRA[3]

1

Low

O

System byte address /

SDRAM address

107

VDDIO

—

Pad Pwr

Digital I/O power, 3.3 V

108

VSSIO

—

Pad Gnd

I/O ground

109

D[24]

1

Low

I/O

Data I/O

110

A[23]/DRA[4]

1

Low

O

System byte address /

SDRAM address

111

D[23]

1

Low

I/O

Data I/O

112

A[22]/DRA[5]

1

Low

O

System byte address /

SDRAM address

113

D[22]

1

Low

I/O

Data I/O

114

A[21]/DRA[6]

1

Low

O

System byte address /

SDRAM address

115

D[21]

1

Low

I/O

Data I/O

116

VSSIO

Pad Gnd

I/O ground

117

A[20]/DRA[7]

1

Low

O

System byte address /

SDRAM address

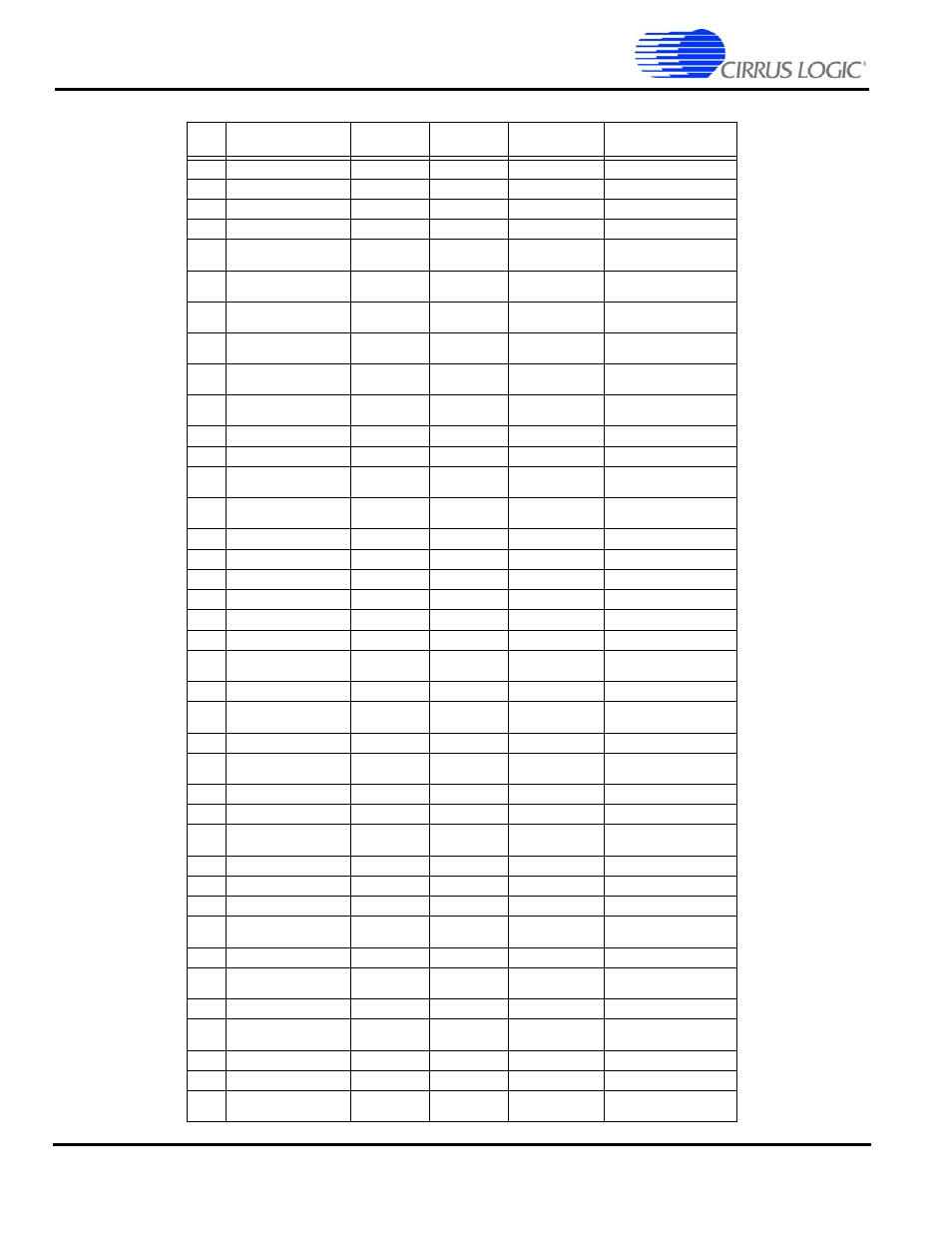

Table 20. 208-Pin LQFP Numeric Pin Listing (Continued)

Pin

No.

Signal

Strength

†

Reset

State

Type

Description