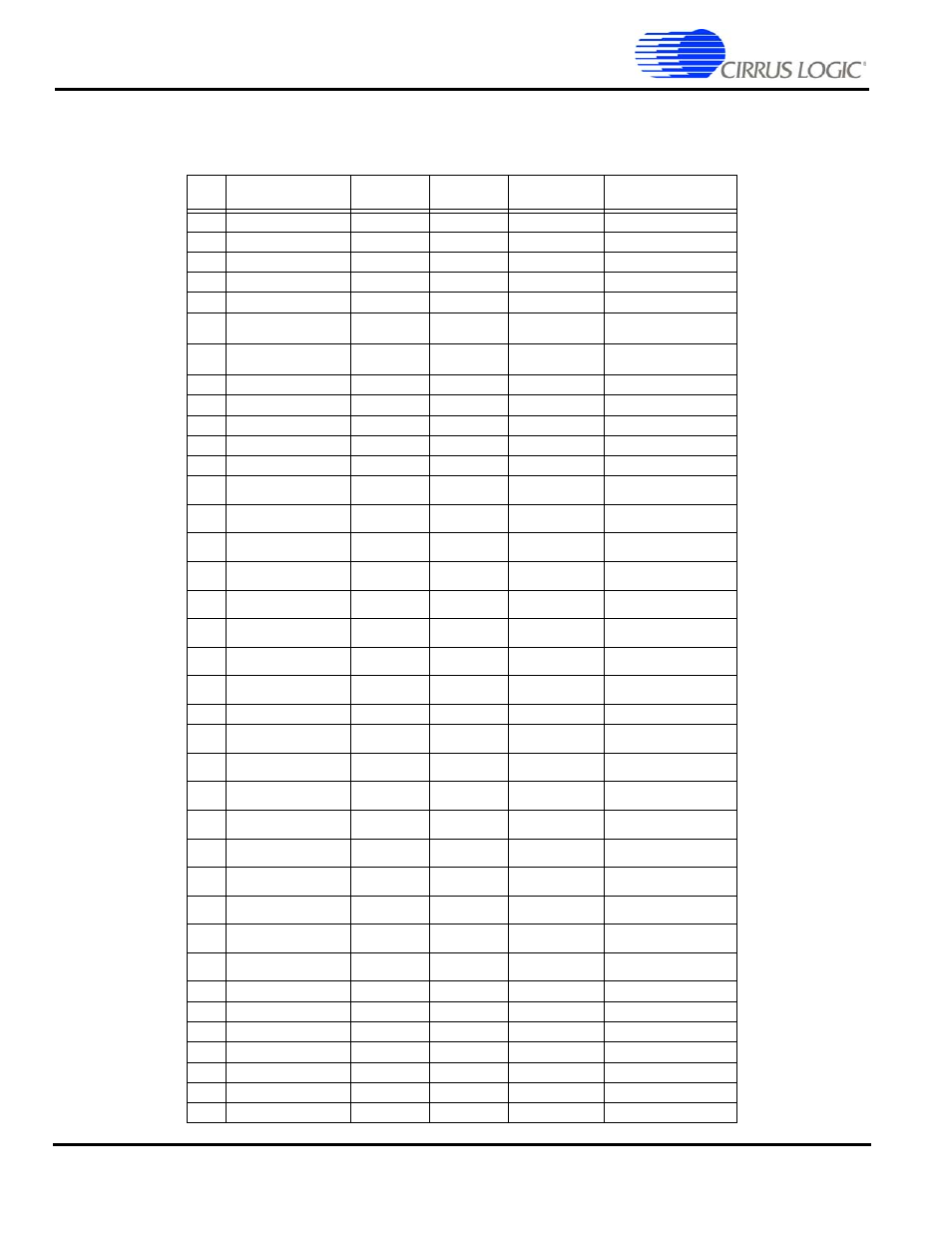

Pin lqfp numeric pin listing, Table 20. 208-pin lqfp numeric pin listing – Cirrus Logic EP7312 User Manual

Page 32

32

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS508F2

EP7312

High-Performance, Low-Power System on Chip

208-Pin LQFP Numeric Pin Listing

Table 20. 208-Pin LQFP Numeric Pin Listing

Pin

No.

Signal

Strength

†

Reset

State

Type

Description

1

nCS[5]

1

Low

O

Chip select 5

2

VDDIO

Pad Pwr

Digital I/O power, 3.3 V

3

VSSIO

Pad Gnd

I/O ground

4

EXPCLK

1

I

Expansion clock input

5

WORD

1

Low

O

Word access select output

6

WRITE/nSDRAS

1

Low

O

Transfer direction / SDRAM

RAS signal output

7

RUN/CLKEN

1

Low

O

Run output / clock enable

output

8

EXPRDY

1

I

Expansion port ready input

9

TXD[2]

1

High

O

UART 2 transmit data output

10

RXD[2]

I

UART 2 receive data input

11

TDI

with p/u*

I

JTAG data input

12

VSSIO

Pad Gnd

I/O ground

13

PB[7]

1

Input

‡

I/O

GPIO port B

14

PB[6]

1

Input

‡

I/O

GPIO port B

15

PB[5]

1

Input

‡

I/O

GPIO port B

16

PB[4]

1

Input

‡

I/O

GPIO port B

17

PB[3]

1

Input

‡

I/O

GPIO port B

18

PB[2]

1

Input

‡

I/O

GPIO port B

19

PB[1]

1

Input

‡

I/O

GPIO port B

20

PB[0]

1

Input

‡

I/O

GPIO port B

21

VDDIO

Pad Pwr

Digital I/O power, 3.3 V

22

TDO

1

Input

‡

O

JTAG data out

23

PA[7]

1

Input

‡

I/O

GPIO port A

24

PA[6]

1

Input

‡

I/O

GPIO port A

25

PA[5]

1

Input

‡

I/O

GPIO port A

26

PA[4]

1

Input

‡

I/O

GPIO port A

27

PA[3]

1

Input

‡

I/O

GPIO port A

28

PA[2]

1

Input

‡

I/O

GPIO port A

29

PA[1]

1

Input

‡

I/O

GPIO port A

30

PA[0]

1

Input

‡

I/O

GPIO port A

31

LEDDRV

1

Low

O

IR LED drive

32

TXD[1]

1

High

O

UART 1 transmit data out

33

VSSIO

1

High

Pad Gnd

I/O ground

34

PHDIN

I

Photodiode input

35

CTS

I

UART 1 clear to send input

36

RXD[1]

I

UART 1 receive data input

37

DCD

I

UART 1 data carrier detect