Ds508f2 – Cirrus Logic EP7312 User Manual

Page 33

DS508F2

Copyright Cirrus Logic, Inc. 2011

(All Rights Reserved)

33

EP7312

High-Performance, Low-Power System on Chip

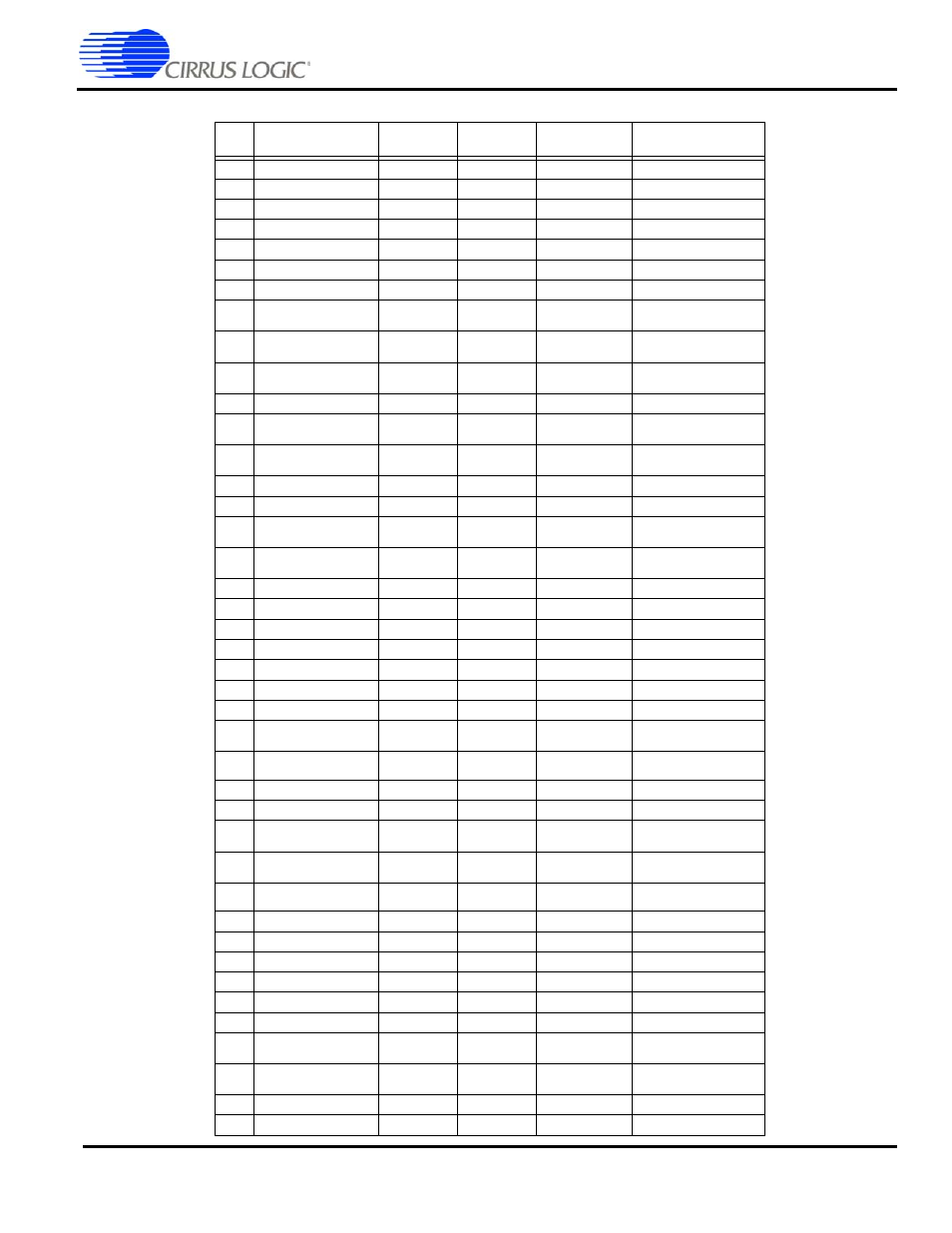

38

DSR

I

UART 1 data set ready input

39

nTEST[1]

With p/u*

I

Test mode select input

40

nTEST[0]

With p/u*

I

Test mode select input

41

EINT[3]

I

External interrupt

42

nEINT[2]

I

External interrupt input

43

nEINT[1]

I

External interrupt input

44

nEXTFIQ

I

External fast interrupt input

45

PE[2]/CLKSEL

1

Input

‡

I/O

GPIO port E / clock input

mode select

46

PE[1]/BOOTSEL[1]

1

Input

‡

I/O

GPIO port E / boot mode

select

47

PE[0]/BOOTSEL[0]

1

Input

‡

I/O

GPIO port E / Boot mode

select

48

VSSRTC

RTC Gnd

Real time clock ground

49

RTCOUT

O

Real time clock oscillator

output

50

RTCIN

I

Real time clock oscillator

input

51

VDDRTC

RTC power

Real time clock power, 2.5 V

52

N/C

53

PD[7]/SDQM[1]

1

Low

I/O

GPIO port D / SDRAM byte

lane mask

54

PD[6]/SDQM[0]

1

Low

I/O

GPIO port D / SDRAM byte

lane mask

55

PD[5]

1

Low

I/O

GPIO port D

56

PD[4]

1

Low

I/O

GPIO port D

57

VDDIO

Pad Pwr

Digital I/O power, 3.3 V

58

TMS

with p/u*

I

JTAG mode select

59

PD[3]

1

Low

I/O

GPIO port D

60

PD[2]

1

Low

I/O

GPIO port D

61

PD[1]

1

Low

I/O

GPIO port D

62

PD[0]/LEDFLSH

1

Low

I/O

GPIO port D / LED blinker

output

63

SSICLK

1

Input

‡

I/O

DAI/CODEC/SSI2 serial clock

64

VSSIO

Pad Gnd

I/O ground

65

SSITXFR

1

Low

I/O

DAI/CODEC/SSI2 serial clock

66

SSITXDA

1

Low

O

DAI/CODEC/SSI2 serial data

output

67

SSIRXDA

I

DAI/CODEC/SSI2 serial data

input

68

SSIRXFR

Input

‡

I/O

DAI/CODEC/SSI2 frame sync

69

ADCIN

I

SSI1 ADC serial input

70

nADCCS

1

High

O

SSI1 ADC chip select

71

VSSCORE

Core ground

Core ground

72

VDDCORE

Core Pwr

Core power, 2.5 V

73

VSSIO

Pad Gnd

I/O ground

74

VDDIO

Pad Pwr

Digital I/O power, 3.3 V

75

DRIVE[1]

2

High /

Low

I/O PWM

drive

output

76

DRIVE[0]

2

High /

Low

I/O PWM

drive

output

77

ADCCLK

1

Low

O

SSI1 ADC serial clock

78

ADCOUT

1

Low

O

SSI1 ADC serial data output

Table 20. 208-Pin LQFP Numeric Pin Listing (Continued)

Pin

No.

Signal

Strength

†

Reset

State

Type

Description