Cirrus Logic CS8421 User Manual

Cs8421, Bit, 192-khz asynchronous sample rate converter, Features

Copyright

Cirrus Logic, Inc. 2012

(All Rights Reserved)

32-bit, 192-kHz Asynchronous Sample Rate Converter

Features

175 dB Dynamic Range

–140 dB THD+N

No Programming Required

No External Master Clock Required

Supports Sample Rates up to 211 kHz

Input/Output Sample Rate Ratios of 7.5:1 to 1:8

Master Clock Support for 128 x Fs, 256 x Fs,

384 x Fs, and 512 x Fs (Master Mode)

16-, 20-, 24-, or 32-bit Data I/O

32-bit Internal Signal Processing

Dither Automatically Applied and Scaled to

Output Resolution

Flexible 3-wire Serial Digital Audio Input and

Output Ports

Master and Slave Modes for Both Input and

Output

Bypass Mode

Time Division Multiplexing (TDM) Mode

Attenuates Clock Jitter

Multiple Device Outputs are Phase Matched

Linear Phase FIR Filter

Automatic Soft Mute/Unmute

+2.5 V Digital Supply (VD)

+3.3 V or 5.0 V Digital Interface (VL)

Space-saving 20-pin TSSOP and QFN

Packages

The CS8421 supports sample rates up to 211 kHz and

is available in 20-pin TSSOP and QFN packages in both

Commercial (-10° to +70°C) and Automotive (-40° to

+85°C and -40° to +105°C) grades. The CDB8421 Cus-

tomer Demonstration board is also available for device

evaluation and implementation suggestions. See

dering Information” on page 35

for complete details.

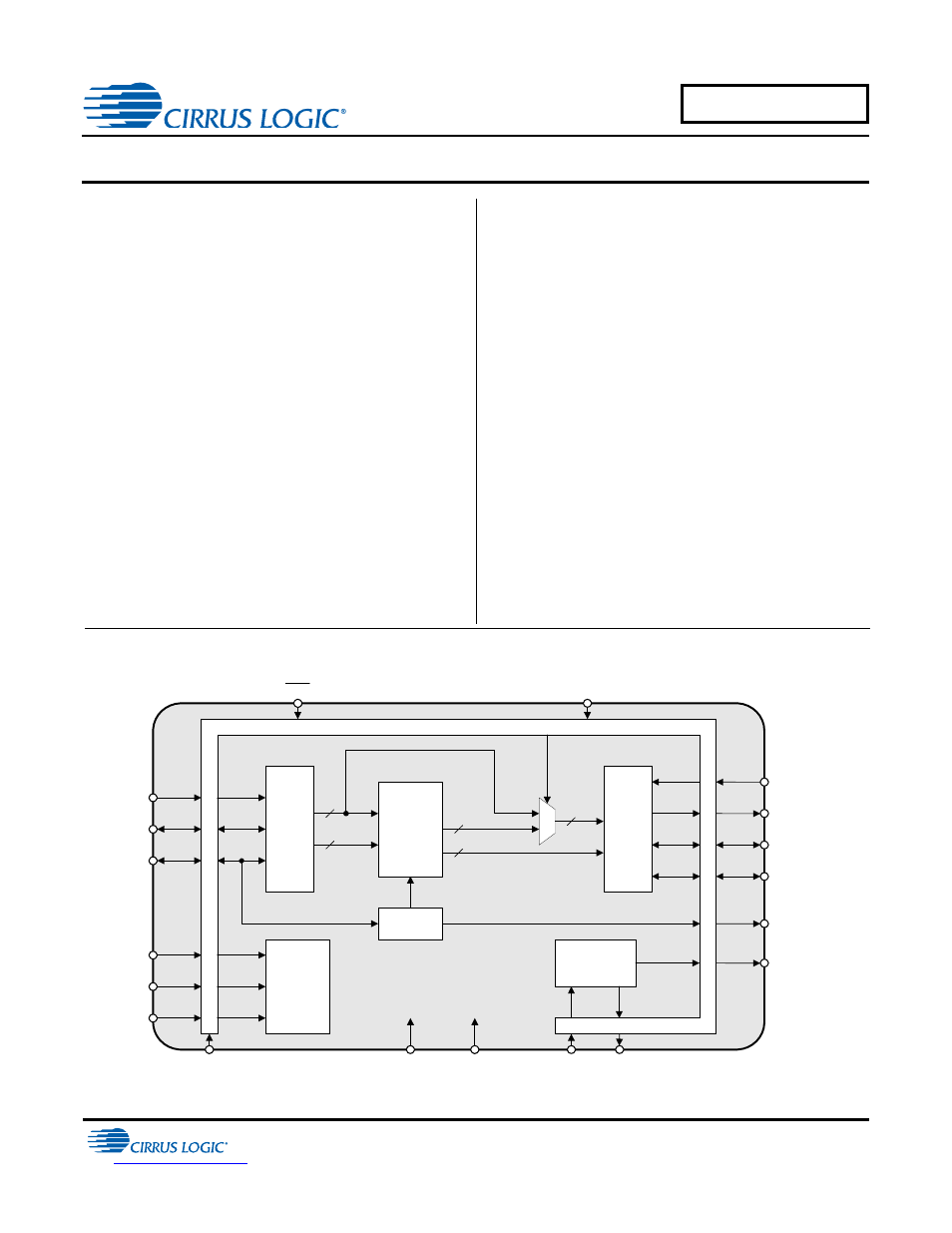

Serial

Audio

Input

Time

Varying

Digital

Filters

BYPASS

Digital

PLL

Clock

Generator

ILRCK

ISCLK

SDIN

Sync Info

Data

Serial

Audio

Output

OLRCK

OSCLK

SDOUT

XTI

XTO

SRC_UNLOCK

2.5 V (VD)

GND

RST

Sync Info

Data

Data

Level Translators

TDM_IN

MS_SEL

SAIF

SAOF

Serial

Port

Mode

Decoder

Level Tr

anslat

or

s

L

evel Tra

n

sl

a

tors

MCLK_OUT

3.3 V or 5.0 V (VL)

JULY ‘12

DS641F6

CS8421

Document Outline

- 1. Pin Descriptions

- 2. Characteristics and Specifications

- 3. Typical Connection Diagrams

- 4. Applications

- 5. Performance Plots

- Figure 15. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:48 kHz

- Figure 16. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 44.1 kHz:192 kHz

- Figure 17. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 44.1 kHz:48 kHz

- Figure 18. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:44.1 kHz

- Figure 19. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:96 kHz

- Figure 20. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 96 kHz:48 kHz

- Figure 21. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 192 kHz:48 kHz

- Figure 22. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 48 kHz:96 kHz

- Figure 23. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 48 kHz:48 kHz

- Figure 24. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 44.1 kHz:192 kHz

- Figure 25. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 44.1 kHz:48 kHz

- Figure 26. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 48 kHz:44.1 kHz

- Figure 27. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 96 kHz:48 kHz

- Figure 28. IMD, 10 kHz and 11 kHz -7 dBFS, 96 kHz:48 kHz

- Figure 29. Wideband FFT Plot (16k Points) - 60 dBFS 1 kHz Tone, 192 kHz:48 kHz

- Figure 30. IMD, 10 kHz and 11 kHz -7 dBFS, 48 kHz:44.1 kHz

- Figure 31. IMD, 10 kHz and 11 kHz -7 dBFS, 44.1 kHz:48 kHz

- Figure 32. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 44.1 kHz:48 kHz

- Figure 33. Wideband FFT Plot (16k Points) 0 dBFS 80 kHz Tone, 192 kHz:192 kHz

- Figure 34. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:96 kHz

- Figure 35. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:48 kHz

- Figure 36. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 96 kHz:48 kHz

- Figure 37. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:44.1 kHz

- Figure 38. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 192 kHz

- Figure 39. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 48 kHz

- Figure 40. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 96 kHz

- Figure 41. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 44.1 kHz

- Figure 42. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 192 kHz

- Figure 43. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 32 kHz

- Figure 44. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 32 kHz

- Figure 45. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 96 kHz

- Figure 46. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 44.1 kHz

- Figure 47. Frequency Response with 0 dBFS Input

- Figure 48. Passband Ripple, 192 kHz:48 kHz

- Figure 49. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 48 kHz

- Figure 50. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:48 kHz

- Figure 51. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:44.1 kHz

- Figure 52. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:96 kHz

- Figure 53. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 96 kHz:48 kHz

- Figure 54. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 44.1 kHz:192 kHz

- Figure 55. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 44.1 kHz:48 kHz

- Figure 56. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 192 kHz:44.1 kHz

- Figure 57. THD+N vs. Input Amplitude, 1 kHz Tone, 48 kHz:44.1 kHz

- Figure 58. THD+N vs. Input Amplitude, 1 kHz Tone, 48 kHz:96 kHz

- Figure 59. THD+N vs. Input Amplitude, 1 kHz Tone, 96 kHz:48 kHz

- Figure 60. THD+N vs. Input Amplitude, 1 kHz Tone, 44.1 kHz:192 kHz

- Figure 61. THD+N vs. Input Amplitude, 1 kHz Tone, 44.1 kHz:48 kHz

- Figure 62. THD+N vs. Input Amplitude, 1 kHz Tone, 192 kHz:48 kHz

- Figure 63. THD+N vs. Frequency Input, 0 dBFS, 48 kHz:44.1 kHz

- Figure 64. THD+N vs. Frequency Input, 0 dBFS, 48 kHz:96 kHz

- Figure 65. THD+N vs. Frequency Input, 0 dBFS, 44.1 kHz:48 kHz

- Figure 66. THD+N vs. Frequency Input, 0 dBFS, 96 kHz:48 kHz

- 6. Package Dimensions

- 7. Ordering Information

- 8. Revision History