Switching characteristics (continued), Figure 2. ssc mode - read timing, cs remaining low, Cs5566 – Cirrus Logic CS5566 User Manual

Page 7: Switching characteristics

CS5566

DS806PP2

7

5/4/09

SWITCHING CHARACTERISTICS

(CONTINUED)

T

A

= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V Low; Logic 1 = VD+ = High; CL = 15 pF.

11.

SDO and SCLK will be high impedance when CS is high. In some systems it may require a pull-down resistor.

12.

SCLK = MCLK/2.

Parameter

Symbol Min

Typ

Max

Unit

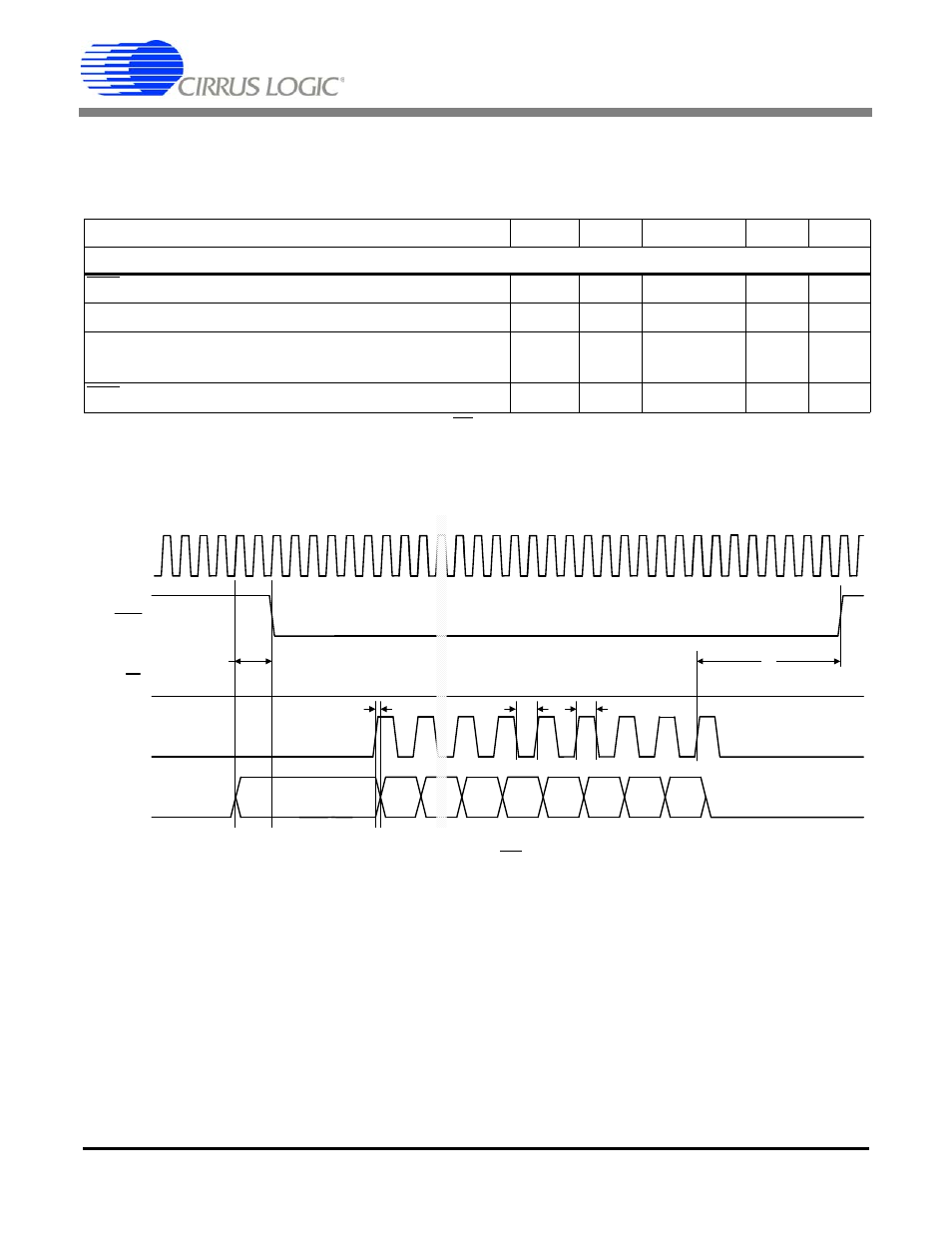

Serial Port Timing in SSC Mode (SMODE = VL)

RDY falling to MSB stable

t

1

-

-2

-

MCLKs

Data hold time after SCLK rising

t

2

-

10

-

ns

Serial Clock (Out)

Pulse Width (low)

(Note 11, 12)

Pulse Width (high)

t

3

t

4

100

100

-

-

-

-

ns

ns

RDY rising after last SCLK rising

t

5

-

8

-

MCLKs

MCLK

RDY

SCLK(o)

SDO

MSB

MSB–1

LSB

LSB+1

CS

t

1

t

2

t

3

t

4

t

5

Figure 2. SSC Mode - Read Timing, CS remaining low (Not to Scale)

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)