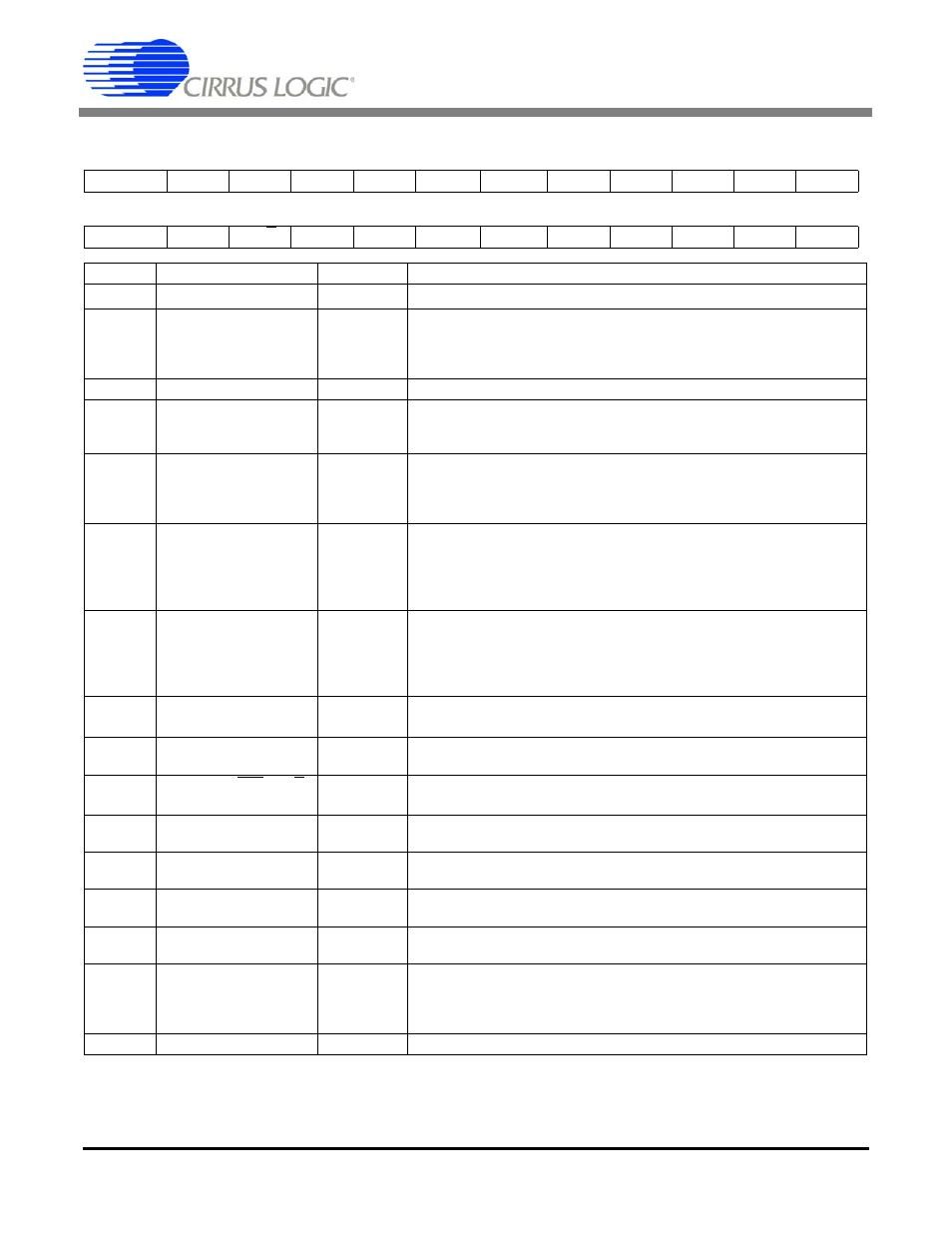

Table 4. configuration register – Cirrus Logic CS5528 User Manual

Page 30

CS5521/22/23/24/28

30

DS317F8

D23(MSB)

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

NU

NU

CFS1

CFS0

NU

MC

LP

RC

DP3

DP2

DP1

DP0

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

PSS

PD

PS/R

LPM

RS

RV

OD

OF

NU

NU

NU

NU

BIT

NAME

VALUE

FUNCTION

D23-D22

Not Used, NU

00

R

1

1.R indicates the bit value after the part is reset.

Must always be logic 0.

D21-D20

Chop Frequency Select,

CFS1-CFS0

00

01

10

11

R 256 Hz Amplifier chop frequency. (XIN = 32.768 kHz)

4,096 Hz Amplifier chop frequency.

16,384 Hz Amplifier chop frequency.

1,024 Hz Amplifier chop frequency.

D19

Not Used, NU

0

R Must always be logic 0.

D18

Multiple Conversion, MC

0

1

R Perform single-Setup conversions. MC bit is ignored during calibrations.

Perform multiple-Setup conversions on Setups in the channel-setup reg-

ister by issuing only one command with MSB = 1.

D17

Loop, LP

0

1

R The conversions on the single Setup (MC = 0) or multiple Setups (MC =

1) are performed only once.

The conversions on the single Setup (MC = 0) or multiple Setups (MC =

1) are continuously performed.

D16

Read Convert, RC

0

1

R Don’t wait for user to finish reading data before starting new conversions.

The RC bit is used in conjunction with the LP bit when the LP bit is set to

logic 1. If LP = 0, the RC bit is ignored. If LP = 1, the ADC waits for user to

read data conversion(s) before converting again. The RC bit is ignored

during calibrations. Refer to Calibration Protocol for details.

D15-D12

Depth Pointer, DP3-DP0

0000

.

.

1111

R When writing or reading the CSRs, these bits (DP3-DP0) determine the

number of CSR’s to be accessed (0000=1). They are also used to deter-

mine how many Setups are converted when MC=1 and a command byte

with its MSB = 1 is issued. Note that the CS5522 has two CSRS, the

CS5524 has four CSRs, and the CS5528 has 8 CSRs.

D11

Power Save Select, PSS

0

2

1

2.When the chip is placed in standby mode, the PD bit (bit D10) should be set to 1.

R Standby Mode (Oscillator active, allows quick power-up).

Sleep Mode (Oscillator inactive).

D10

Pump Disable, PD

0

1

R Charge Pump Enabled.

For PD = 1, the CPD pin goes to a Hi-Z output state.

D9

Power Save/Run, PS/R

0

1

R Run.

Power Save.

D8

Low Power Mode, LPM

0

1

R Normal Mode (LPM bit is only for the CS5522/24/28)

Reduced Power Mode

D7

Reset System, RS

0

1

R Normal Operation.

Activate a Reset cycle. To return to Normal Operation write bit to zero.

D6

Reset Valid, RV

0

1

R

No reset has occurred or bit has been cleared (read only).

Bit is set after a Valid Reset has occurred. (Cleared when read.)

D5

Oscillation Detect, OD

0

1

R Bit is clear when an oscillation condition has not occurred (read only).

Bit is set when an oscillatory condition is detected in the modulator.

D4

Overrange Flag, OF

0

1

R Bit is clear when an overrange condition has not occurred (read only).

Bit is set when input signal is more positive than the positive full scale,

more negative than zero (unipolar mode), or when the input is more neg-

ative than the negative full scale (bipolar mode).

D3-D0

Not Used, NU

0000

R Must always be logic 0.

Table 4. Configuration Register