Cirrus Logic CS5480 User Manual

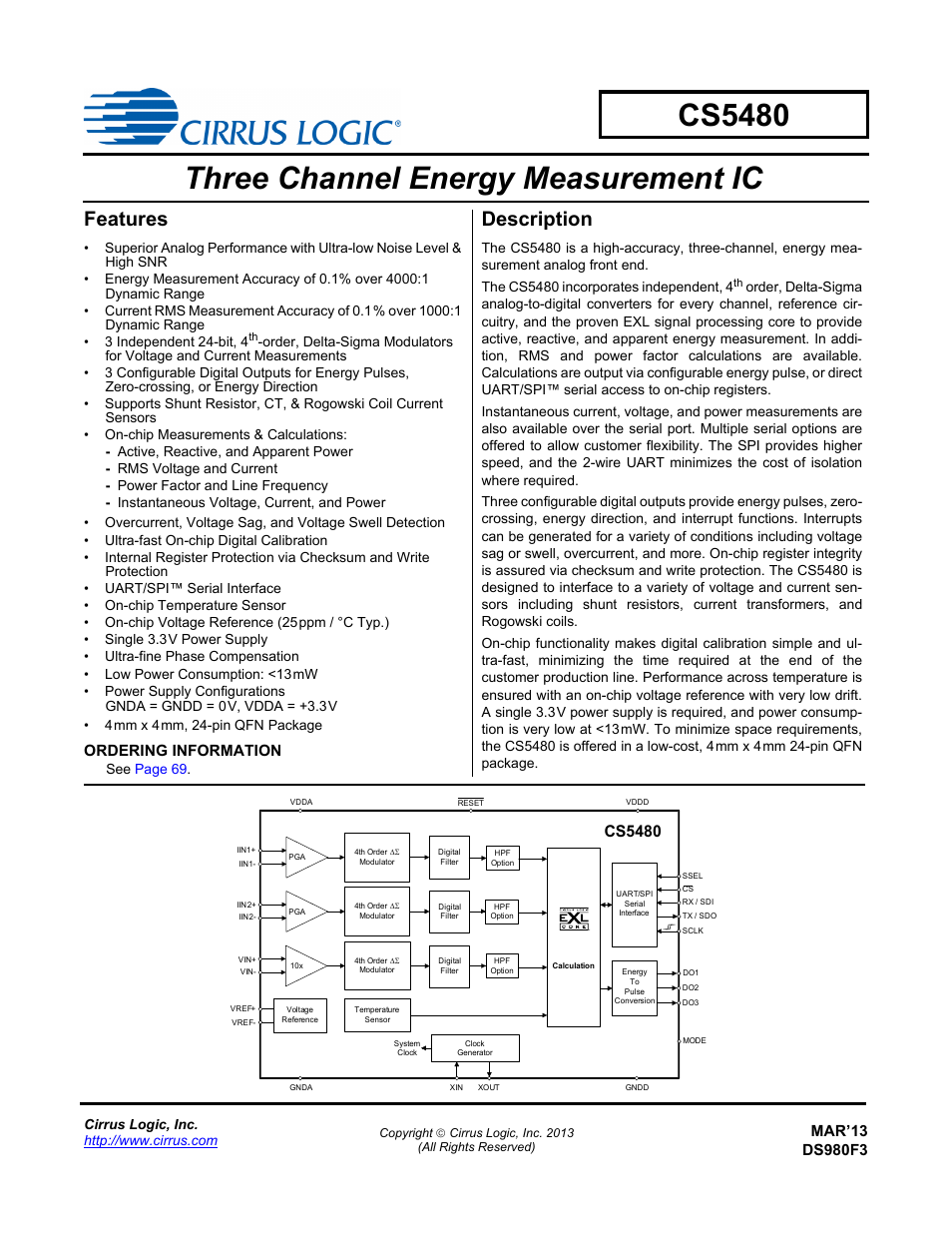

Cs5480 three channel energy measurement ic, Features, Description

Table of contents

Document Outline

- Features

- 1. Overview

- 2. Pin Description

- 3. Characteristics and Specifications

- 4. Signal Flow Description

- 5. Functional Description

- 5.1 Power-on Reset

- 5.2 Power Saving Modes

- 5.3 Zero-crossing Detection

- 5.4 Line Frequency Measurement

- 5.5 Meter Configuration Modes

- 5.6 Tamper Detection and Correction

- 5.7 Energy Pulse Generation

- 5.8 Voltage Sag, Voltage Swell, and Overcurrent Detection

- 5.9 Phase Sequence Detection

- 5.10 Temperature Measurement

- 5.11 Anti-Creep

- 5.12 Register Protection

- 6. Host Commands and Registers

- 6.1 Host Commands

- 6.2 Hardware Registers Summary (Page 0)

- 6.3 Software Registers Summary (Page 16)

- 6.4 Software Registers Summary (Page 17)

- 6.5 Software Registers Summary (Page 18)

- 6.6 Register Descriptions

- 6.6.1 Configuration 0 (Config0) – Page 0, Address 0

- 6.6.2 Configuration 1 (Config1) – Page 0, Address 1

- 6.6.3 Configuration 2 (Config2) – Page 16, Address 0

- 6.6.4 Phase Compensation (PC) – Page 0, Address 5

- 6.6.5 UART Control (SerialCtrl) – Page 0, Address 7

- 6.6.6 Pulse Output Width (PulseWidth) – Page 0, Address 8

- 6.6.7 Zero crossing Number (ZXNUM) – Page 0, Address 55

- 6.6.8 Energy Pulse Rate (PulseRate) – Page 18, Address 28

- 6.6.9 Pulse Output Control (PulseCtrl) – Page 0, Address 9

- 6.6.10 Register Lock Control (RegLock) – Page 0, Address 34

- 6.6.11 Phase Sequence Detection and Control (PSDC) – Page 0, Address 48

- 6.6.12 Checksum of Critical Registers (RegChk) – Page 16, Address 1

- 6.6.13 Interrupt Status (Status0) – Page 0, Address 23

- 6.6.14 Interrupt Mask ( Mask ) – Page 0, Address 3

- 6.6.15 Chip Status 1 (Status1) – Page 0, Address 24

- 6.6.16 Chip Status 2 (Status2) – Page 0, Address 25

- 6.6.17 Line to Sample Frequency Ratio (Epsilon) – Page 16, Address 49

- 6.6.18 Automatic Channel Select Level ( IchanLEVEL ) – Page 16, Address 50

- 6.6.19 Current Channel Minimum Amplitude (PMIN (IRMSMIN)) – Page 16, Address 56

- 6.6.20 No Load Threshold (LoadMIN) – Page 16, Address 58

- 6.6.21 Voltage Fixed RMS Reference (VFRMS ) – Page 16, Address 59

- 6.6.22 Sample Count (SampleCount) – Page 16, Address 51

- 6.6.23 Cycle Count (CycleCount) – Page 18, Address 62

- 6.6.24 Filter Settling Time for Conversion Startup (TSETTLE) – Page 16, Address 57

- 6.6.25 System Gain (SysGAIN) – Page 16, Address 60

- 6.6.26 Rogowski Coil Integrator Gain (IntGAIN) – Page 18, Address 43

- 6.6.27 System Time (Time) – Page 16, Address 61

- 6.6.28 Voltage 1 Sag Duration (V1SagDUR ) – Page 17, Address 0

- 6.6.29 Voltage 1 Sag Level (V1SagLEVEL ) – Page 17, Address 1

- 6.6.30 Current 1 Overcurrent Duration (I1OverDUR ) – Page 17, Address 4

- 6.6.31 Current 1 Overcurrent Level (I1OverLEVEL ) – Page 17, Address 5

- 6.6.32 Voltage 2 Sag Duration (V2SagDUR ) – Page 17, Address 8

- 6.6.33 Voltage 2 Sag Level (V2SagLEVEL ) – Page 17, Address 9

- 6.6.34 Current 2 Overcurrent Duration (I2OverDUR ) – Page 17, Address 12

- 6.6.35 Current 2 Overcurrent Level (I2OverLEVEL ) – Page 17, Address 13

- 6.6.36 Voltage 1 Swell Duration (V1SwellDUR ) – Page 18, Address 46

- 6.6.37 Voltage 1 Swell Level (V1SwellLEVEL ) – Page 18, Address 47

- 6.6.38 Voltage 2 Swell Duration (V2SwellDUR ) – Page 18, Address 50

- 6.6.39 Voltage 2 Swell Level (V2SwellLEVEL ) – Page 18, Address 51

- 6.6.40 Instantaneous Current 1 (I1) – Page 16, Address 2

- 6.6.41 Instantaneous Voltage 1 (V1) – Page 16, Address 3

- 6.6.42 Instantaneous Active Power 1 (P1) – Page 16, Address 4

- 6.6.43 Active Power 1 (P1AVG) – Page 16, Address 5

- 6.6.44 RMS Current 1 (I1RMS ) – Page 16, Address 6

- 6.6.45 RMS Voltage 1 (V1RMS ) – Page 16, Address 7

- 6.6.46 Instantaneous Current 2 (I2) – Page 16, Address 8

- 6.6.47 Instantaneous Voltage 2 (V2) – Page 16, Address 9

- 6.6.48 Instantaneous Active Power 2 (P2) – Page 16, Address 10

- 6.6.49 Active Power 2 (P2AVG ) – Page 16, Address 11

- 6.6.50 RMS Current 2 (I2RMS) – Page 16, Address 12

- 6.6.51 RMS Voltage 2 (V2RMS ) – Page 16, Address 13

- 6.6.52 Reactive Power 1 (Q1Avg ) – Page 16, Address 14

- 6.6.53 Instantaneous Quadrature Power 1 (Q1) – Page 16, Address 15

- 6.6.54 Reactive Power 2 (Q2Avg ) – Page 16, Address 16

- 6.6.55 Instantaneous Quadrature Power 2 (Q2) – Page 16, Address 17

- 6.6.56 Peak Current 1 (I1PEAK) – Page 0, Address 37

- 6.6.57 Peak Voltage 1 (V1PEAK) – Page 0, Address 36

- 6.6.58 Apparent Power 1 (S1) – Page 16, Address 20

- 6.6.59 Power Factor 1 (PF1) – Page 16, Address 21

- 6.6.60 Peak Current 2 (I2PEAK) – Page 0, Address 39

- 6.6.61 Peak Voltage 2 (V2PEAK) – Page 0, Address 38

- 6.6.62 Apparent Power 2 (S2) – Page 16, Address 24

- 6.6.63 Power Factor 2 (PF2) – Page 16, Address 25

- 6.6.64 Temperature (T) – Page 16, Address 27

- 6.6.65 Total Active Power (PSUM ) – Page 16, Address 29

- 6.6.66 Total Apparent Power (SSUM ) – Page 16, Address 30

- 6.6.67 Total Reactive Power (QSUM ) – Page 16, Address 31

- 6.6.68 DC Offset for Current (I1DCOFF , I2DCOFF ) – Page 16, Address 32, 39

- 6.6.69 DC Offset for Voltage (V1DCOFF , V2DCOFF ) – Page 16, Address 34, 41

- 6.6.70 Gain for Current (I1GAIN , I2GAIN ) – Page 16, Address 33, 40

- 6.6.71 Gain for Voltage (V1GAIN , V2GAIN ) – Page 16, Address 35, 42

- 6.6.72 Average Active Power Offset (P1OFF, P2OFF ) – Page 16, Address 36, 43

- 6.6.73 Average Reactive Power Offset (Q1OFF , Q2OFF ) – Page 16, Address 38, 45

- 6.6.74 AC Offset for Current (I1ACOFF, I 2ACOFF ) – Page 16, Address 37, 44

- 6.6.75 Temperature Gain (TGAIN ) – Page 16, Address 54

- 6.6.76 Temperature Offset (TOFF ) – Page 16, Address 55

- 6.6.77 Calibration Scale (Scale) – Page18, Address 63

- 6.6.78 V-channel Zero-crossing Threshold (VZXLEVEL) – Page 18, Address 58

- 6.6.79 I-channel Zero-crossing Threshold (IZXLEVEL) – Page 18, Address 24

- 7. System Calibration

- 8. Basic Application Circuits

- 9. Package Dimensions

- 10. Ordering Information

- 11. Environmental, Manufacturing, and Handling Information

- 12. Revision History