1 spi, 2 uart, 4 mode pin – Cirrus Logic CS5480 User Manual

Page 8: 1 spi 2.2.3.2 uart, Cs5480

CS5480

8

DS980F3

2.2.3.1 SPI

The CS5480 provides a Serial Peripheral Interface

(SPI) that operates as a slave device in 4-wire mode

and supports multiple slaves on the SPI bus. The 4-wire

SPI includes CS, SCLK, SDI, and SDO signals.

CS is the chip select input for the CS5480 SPI port. A

high logic level de-asserts it, tri-stating the SDO pin and

clearing the SPI interface. A low logic level enables the

SPI port. Although the CS pin may be tied low for

systems that do not require multiple SDO drivers, using

the CS signal is strongly recommended to achieve a

more reliable SPI communication.

SCLK is the serial clock input for the CS5480 SPI port.

Serial data changes as a result of the falling edge of

SCLK and is valid at the rising edge. The SCLK pin is a

Schmitt-trigger input.

SDI is the serial data input to the CS5480.

SDO is the serial data output from the CS5480.

The CS5480 SPI transmits and receives data MSB first.

Refer to

on page 14 and

on page 15 for more detailed information of

SPI timing.

2.2.3.2 UART

The CS5480 device contains an asynchronous,

full-duplex UART. The UART may be used in either

standard 2-wire communication mode (RX/TX) for

connecting a single device or 3-wire communication

mode (RX/TX/CS) for connecting multiple devices.

When connecting a single CS5480 device, CS should

be held low to enable the UART. Multiple CS5480

devices can communicate to the same master UART in

the 3-wire mode by pulling a slave CS pin low during

data transmissions. Common RX and TX signals are

provided to all the slave devices, and each slave device

requires a separate CS signal for enabling

communication to that slave. The multi-device UART

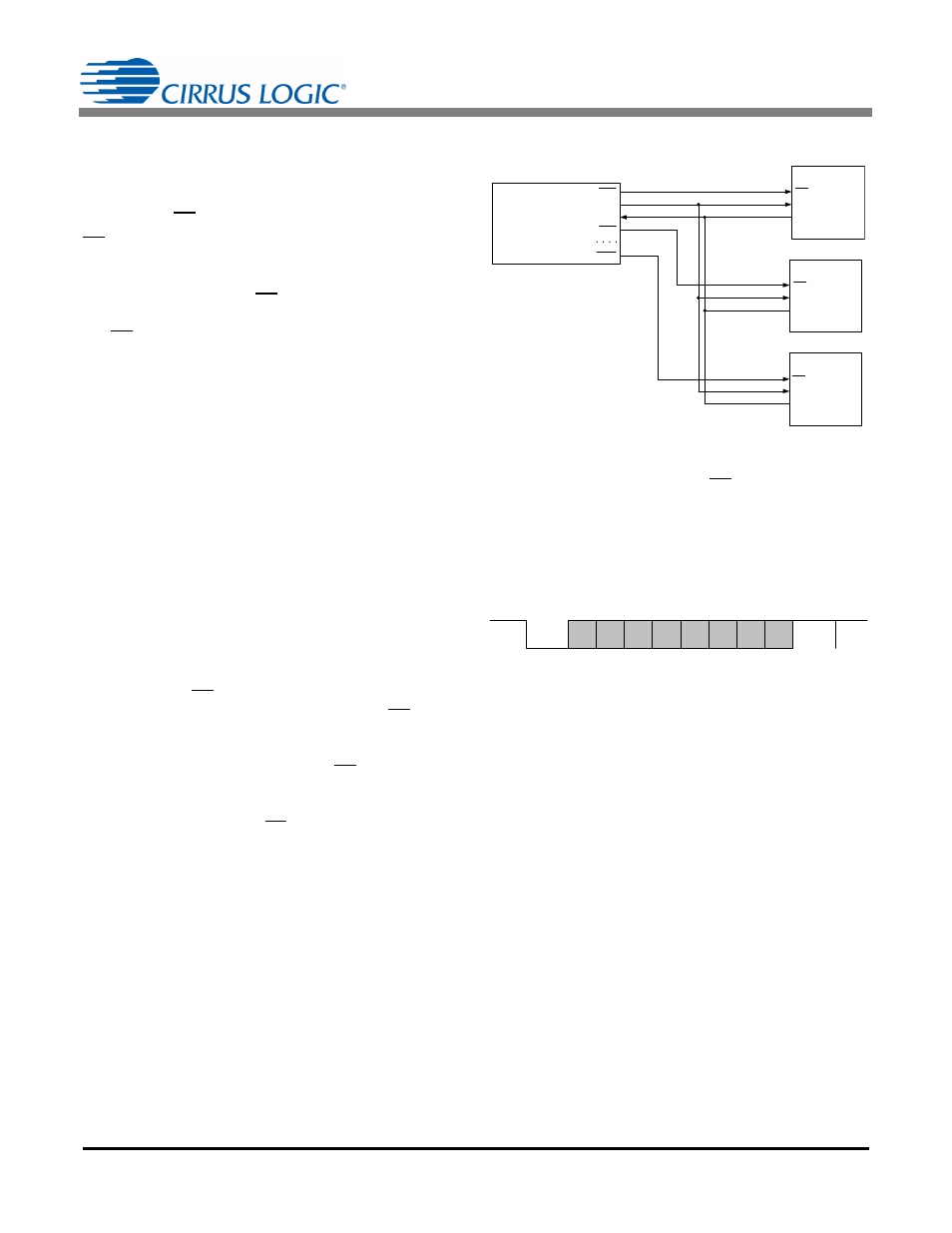

mode connections are shown in Figure 2.

Figure 2. Multi-device UART Connections

The multi-device UART mode timing diagram provides

the timing requirements for the CS control (see

The CS5480 UART operates in 8-bit mode, which

transmits a total of 10 bits per byte. Data is transmitted

and received LSB first, with one start bit, eight data bits,

and one stop bit.

Figure 3. UART Serial Frame Format

The baud rate is defined in the SerialCtrl register. After

chip reset, the default baud rate is 600, if MCLK is

4.096MHz. The baud rate is based on the contents of

bits BR[15:0] in the SerialCtrl register and is calculated

as follows:

BR[15:0] = Baud Rate x (524288/MCLK)

or

Baud Rate = BR[15:0] / (524288/MCLK)

The maximum baud rate is 512K if MCLK is 4.096MHz.

2.2.4 MODE Pin

The MODE pin must be tied to VDDA for normal

operation. The MODE pin is used primarily for factory

test procedures.

UART

MASTER

SLAVE 0

SLAVE 1

SLAVE N

CS

RX

TX

CS

RX

TX

CS

RX

TX

CS0

CS1

CSN

RX

TX

0

1

2

7

IDLE

STOP

3

4

5

6

START

DATA

IDLE