Cs5480 – Cirrus Logic CS5480 User Manual

Page 48

CS5480

48

DS980F3

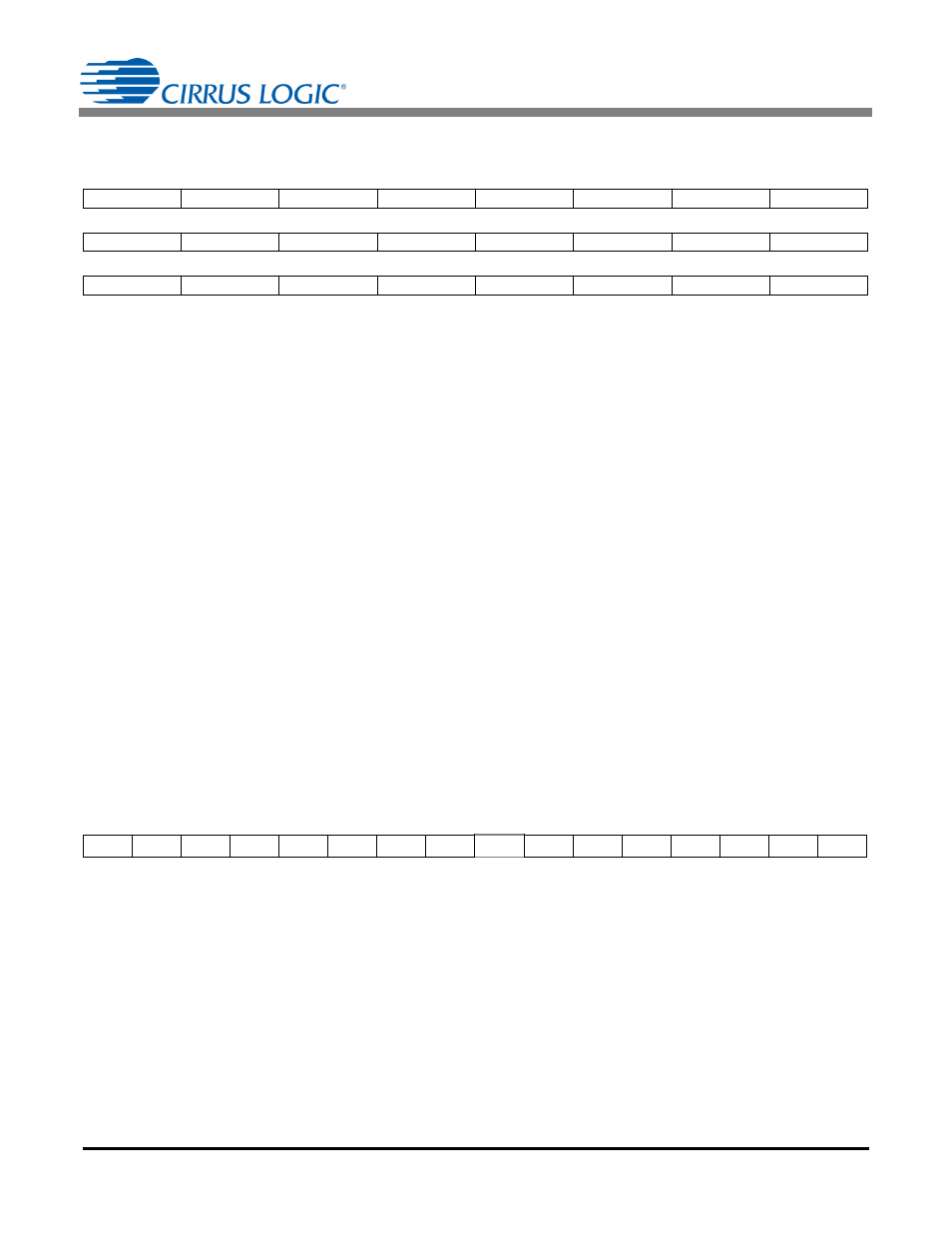

6.6.16 Chip Status 2 (Status2) – Page 0, Address 25

Default = 0x00 0000

This register indicates a variety of conditions within the chip.

[23:6]

Reserved.

QSUM_SIGN

Indicates the sign of the value contained in Q

SUM

.

0 = positive value

1 = negative value

Q2_SIGN

Indicates the sign of the value contained in Q2

AVG

.

0 = positive value

1 = negative value

Q1_SIGN

Indicates the sign of the value contained in Q1

AVG

.

0 = positive value

1 = negative value

PSUM_SIGN

Indicates the sign of the value contained in P

SUM

.

0 = positive value

1 = negative value

P2_SIGN

Indicates the sign of the value contained in P2

AVG

.

0 = positive value

1 = negative value

P1_SIGN

Indicates the sign of the value contained in P1

AVG

.

0 = positive value

1 = negative value

6.6.17 Line to Sample Frequency Ratio (Epsilon)

–

Page 16, Address 49

Default = 0x01 999A (0.0125 or 50Hz/4.0kHz)

Epsilon is the ratio of the input line frequency to the OWR.

It can either be written by the application program or calculated automatically from the line frequency (from

the voltage channel 1 input) using the AFC bit in the Config2 register. It is a two's complement value in the

range of -1.0

value1.0, with the binary point to the right of the MSB. Negative values are not used.

23

22

21

20

19

18

17

16

-

-

-

-

-

-

-

-

15

14

13

12

11

10

9

8

-

-

-

-

-

-

-

-

7

6

5

4

3

2

1

0

-

-

QSUM_SIGN

Q2_SIGN

Q1_SIGN

PSUM_SIGN

P2_SIGN

P1_SIGN

MSB

LSB

-(2

0

)

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

.....

2

-17

2

-18

2

-19

2

-20

2

-21

2

-22

2

-23