Switching characteristics, Start-up, Spi timing – Cirrus Logic CS5480 User Manual

Page 14: Uart timing, Refer to, Cs5480

CS5480

14

DS980F3

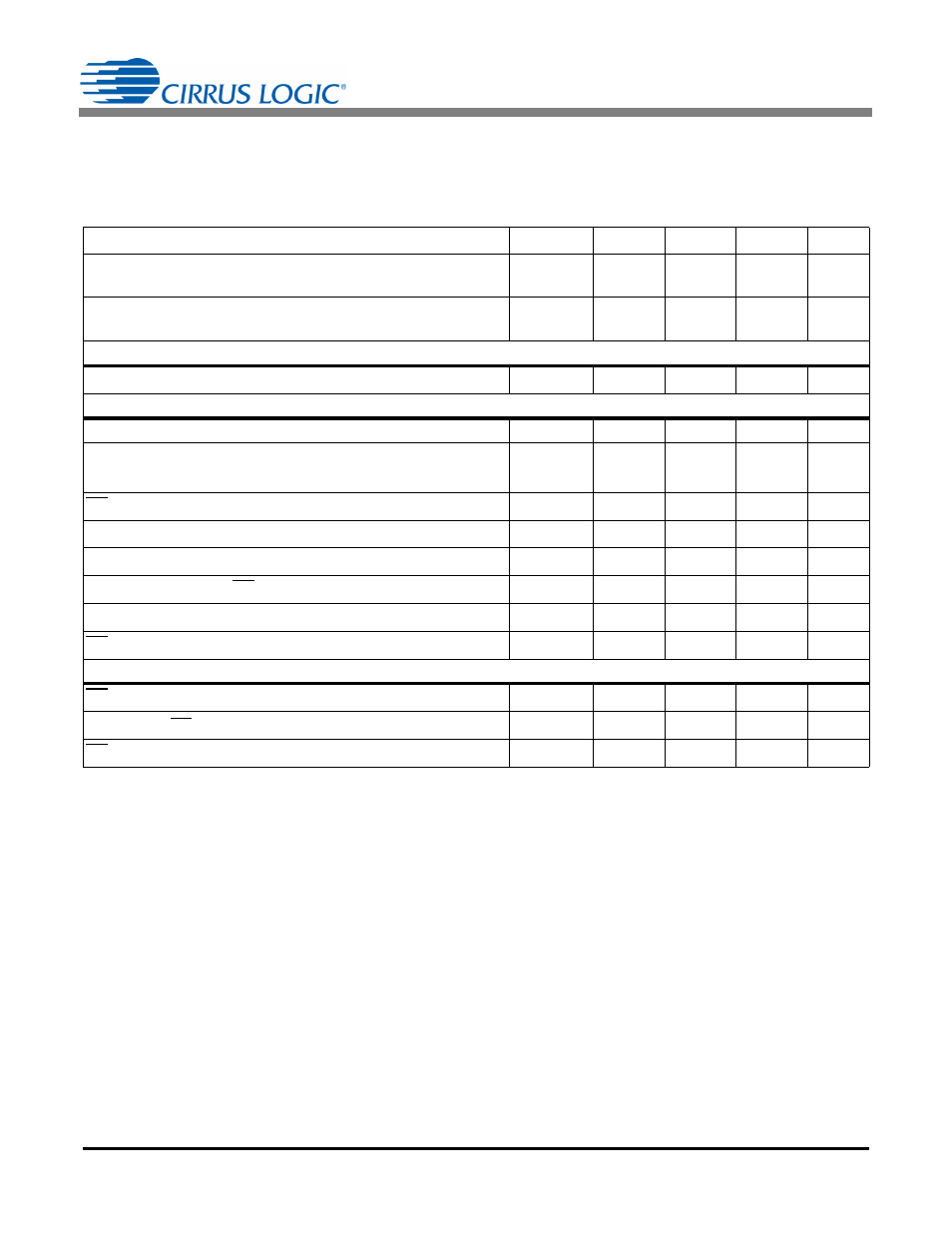

SWITCHING CHARACTERISTICS

• Min / Max characteristics and specifications are guaranteed over all

Recommended Operating Conditions

• Typical characteristics and specifications are measured at nominal supply voltages and T

A

= 25°C.

• VDDA = +3.3V ±10%; GNDA = GNDD = 0V. All voltages with respect to 0V.

• Logic Levels: Logic 0 = 0V, Logic 1 = VDDA.

Notes:

13.

Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.

14.

Oscillator start-up time varies with crystal parameters. This specification does not apply when using an external clock source.

15.

The maximum SCLK is 2 MHz during a byte transaction. The minimum 1µs idle time is required on the SCLK between two

consecutive bytes.

Parameter

Symbol Min Typ

Max

Unit

Rise Times

DO1-DO3

Any Digital Output Except DO1-DO3

t

rise

-

-

-

50

1.0

-

µs

ns

Fall Times

DO1-DO3

Any Digital Output Except DO1-DO3

t

fall

-

-

-

50

1.0

-

µs

ns

Start-up

Oscillator Start-up Time

XTAL = 4.096 MHz (Note 14)

t

ost

-

60

-

ms

SPI Timing

Serial Clock Frequency

SCLK

-

-

2

MHz

Serial Clock

Pulse Width High

Pulse Width Low

t

1

t

2

200

200

-

-

-

-

ns

ns

CS Enable to SCLK Falling

t

3

50

-

-

ns

Data Set-up Time prior to SCLK Rising

t

4

50

-

-

ns

Data Hold Time After SCLK Rising

t

5

100

-

-

ns

SCLK Rising Prior to CS Disable

t

6

1

-

-

µs

SCLK Falling to New Data Bit

t

7

-

-

150

ns

CS Rising to SDO Hi-Z

t

8

-

-

250

ns

UART Timing

CS Enable to RX START bit

t

9

5

-

-

ns

STOP bit to CS Disable

t

10

1

-

-

µs

CS Disable to TX IDLE Hold Time

t

11

-

-

250

ns