Signal flow description, 1 analog-to-digital converters, 2 decimation filters – Cirrus Logic CS5480 User Manual

Page 17: 3 iir filters, Cs5480

CS5480

DS980F3

17

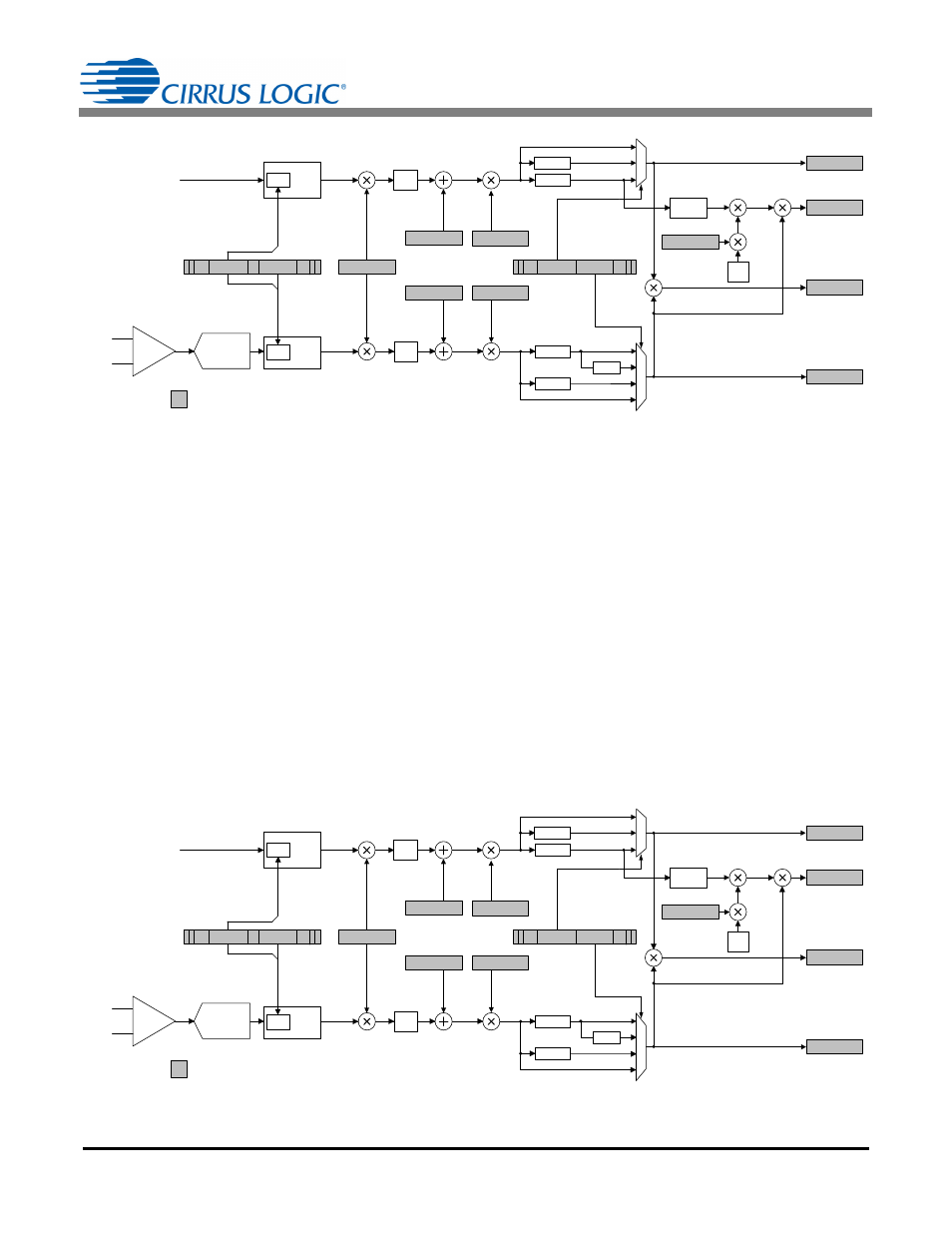

4. SIGNAL FLOW DESCRIPTION

The signal flow for voltage measurement, current

measurement, and the other calculations is shown in

,

, and

.

The signal flow consists of two current channels and a

voltage channel. Even though the CS5480 has only one

voltage channel or voltage analog signal input, there are

two separate voltage digital signal paths (V1 and V2).

Both V1 and V2 come from the same ADC output. Each

current and voltage channel has its own differential

input pin.

4.1 Analog-to-Digital Converters

All three input channels use fourth-order delta-sigma

modulators to convert the analog inputs to single-bit

digital data streams. The converters sample at a rate of

MCLK/8. This high sampling provides a wide dynamic

range and simplifies anti-alias filter design.

4.2 Decimation Filters

The single-bit modulator output data is widened to 24

bits and down sampled to MCLK/1024 with low-pass

decimation filters. These decimation filters are

third-order Sinc filters. The outputs of the filters are

passed through an IIR "anti-sinc" filter.

4.3 IIR Filters

The IIR filters are used to compensate for the amplitude

roll-off of the decimation filters. The droop-correction

filter flattens the magnitude response of the channel out

to the Nyquist frequency, thus allowing for accurate

measurements of up to 2kHz (MCLK = 4.096MHz). By

default, the IIR filters are enabled. The IIR filters can be

bypassed by setting the IIR_OFF bit in the Config2

register.

MU

X

SINC

3

IIN2±

SINC

3

PGA

HPF

DELAY

CTRL

2

MU

X

PMF

HPF

PMF

IIR

Phase

Shift

Config 2

DELAY

CTRL

INT

Registers

Q2

V2

P2

I2

SYS

GAIN

...

...

I2FLT[1:0]

V2FLT[1:0]

V2

DCOFF

I2

DCOFF

I2

GAIN

V2

GAIN

PC

...

...

FPCC2[8:0]

CPCC2[1:0]

...

IIR

Epsilon

From V Channel ADC

4

th

Order

Modulator

Figure 9. Signal Flow for V1, I1, P1, Q1 Measurements

MU

X

SINC

3

IIN2±

SINC

3

PGA

HPF

DELAY

CTRL

2

MU

X

PMF

HPF

PMF

IIR

Phase

Shift

Config 2

DELAY

CTRL

INT

Registers

Q2

V2

P2

I2

SYS

GAIN

...

...

I2FLT[1:0]

V2FLT[1:0]

V2

DCOFF

I2

DCOFF

I2

GAIN

V2

GAIN

PC

...

...

FPCC2[8:0]

CPCC2[1:0]

...

IIR

Epsilon

From V Channel ADC

4

th

Order

Modulator

Figure 10. Signal Flow for V2, I2, P2, and Q2 Measurements