Register description, 1 mode control 1 (address 01h), 1 control port enable (cpen) – Cirrus Logic CS4382 User Manual

Page 16: 2 freeze controls (freeze), 3 master clock divide enable (mclkdiv), 4 dac pair disable (dacx_dis)

16

DS514F2

CS4382

4. REGISTER DESCRIPTION

Note:

All registers are read/write in I²C Mode and write-only in SPI, unless otherwise noted.

4.1

Mode Control 1 (Address 01h)

4.1.1

Control Port Enable (CPEN)

Default = 0

0 - Disabled

1 - Enabled

Function:

This bit defaults to 0, allowing the device to power-up in Stand-Alone Mode. The Control Port Mode can

be accessed by setting this bit to 1. This will allow the operation of the device to be controlled by the reg-

isters and the pin definitions will conform to Control Port Mode. To accomplish a clean power-up, the user

should write this bit within 10 ms following the release of Reset.

4.1.2

Freeze Controls (FREEZE)

Default = 0

0 - Disabled

1 - Enabled

Function:

This function allows modifications to be made to the registers without the changes taking effect until the

FREEZE is disabled. To make multiple changes in the Control port registers take effect simultaneously,

enable the FREEZE bit, make all register changes, then Disable the FREEZE bit.

4.1.3

Master Clock Divide Enable (MCLKDIV)

Default = 0

0 - Disabled

1 - Enabled

Function:

The MCLKDIV bit enables a circuit which divides the externally applied MCLK signal by 2 prior to all other

internal circuitry.

4.1.4

DAC Pair Disable (DACx_DIS)

Default = 0

0 - DAC Pair x Enabled

1 - DAC Pair x Disabled

Function:

When the bit is set, the respective DAC channel pair (AOUTAx and AOUTBx) will remain in a reset state.

It is advised that changes to these bits be made while the power-down (PDN) bit is enabled to eliminate

the possibility of audible artifacts.

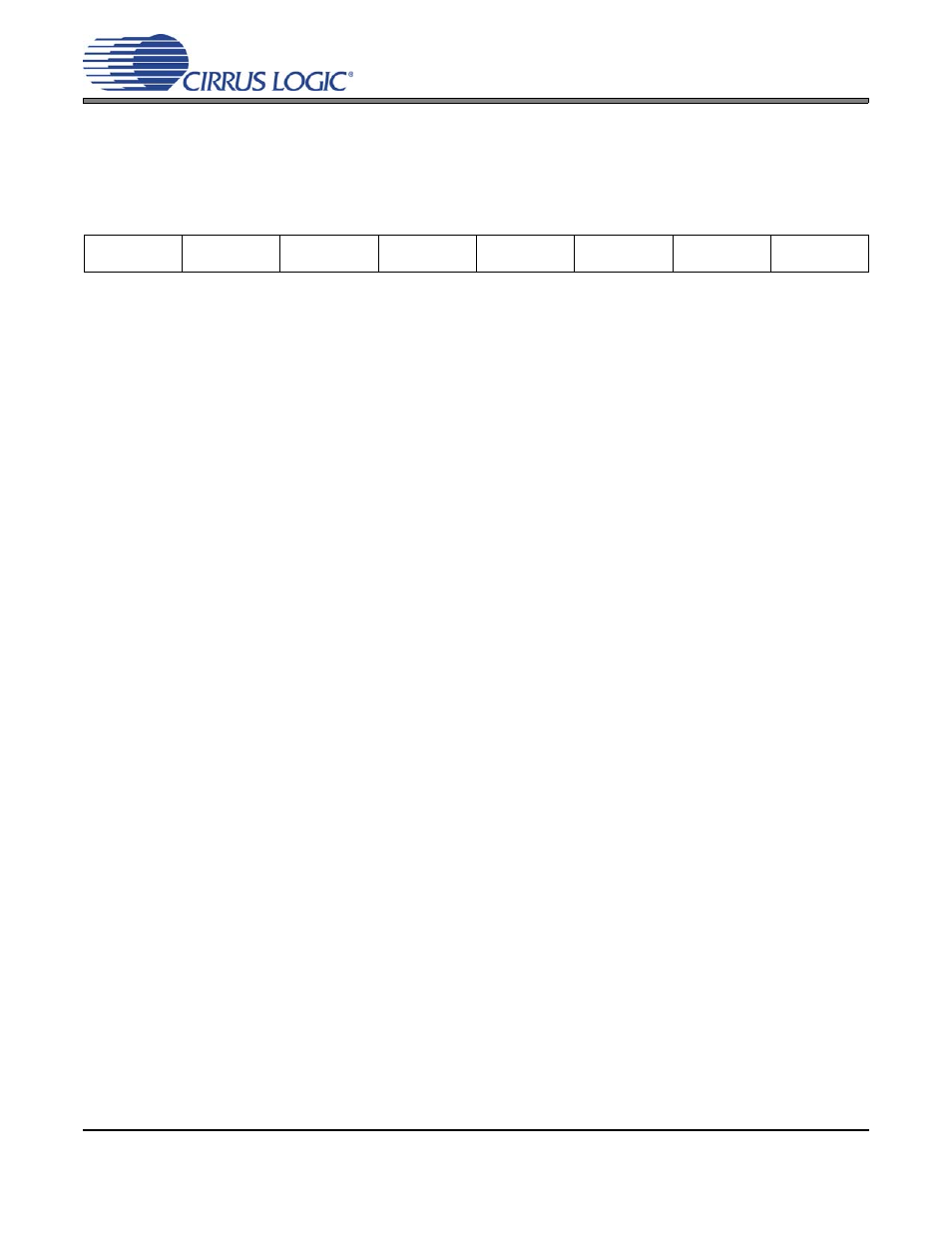

7

6

5

4

3

2

1

0

CPEN

FREEZE

MCLKDIV

DAC4_DIS

DAC3_DIS

DAC2_DIS

DAC1_DIS

PDN

0

0

0

0

0

0

0

1