5 vsp sdin location, 6 vsp sclk source equals mclk, 15 vsp master mode clocking control (address 11h) – Cirrus Logic CS42L73 User Manual

Page 92: 1 vsp master/slave mode, 2 vsp master mode clock control dividers, P 92, Vsp master/slave mode, Cs42l73

92

DS882F1

CS42L73

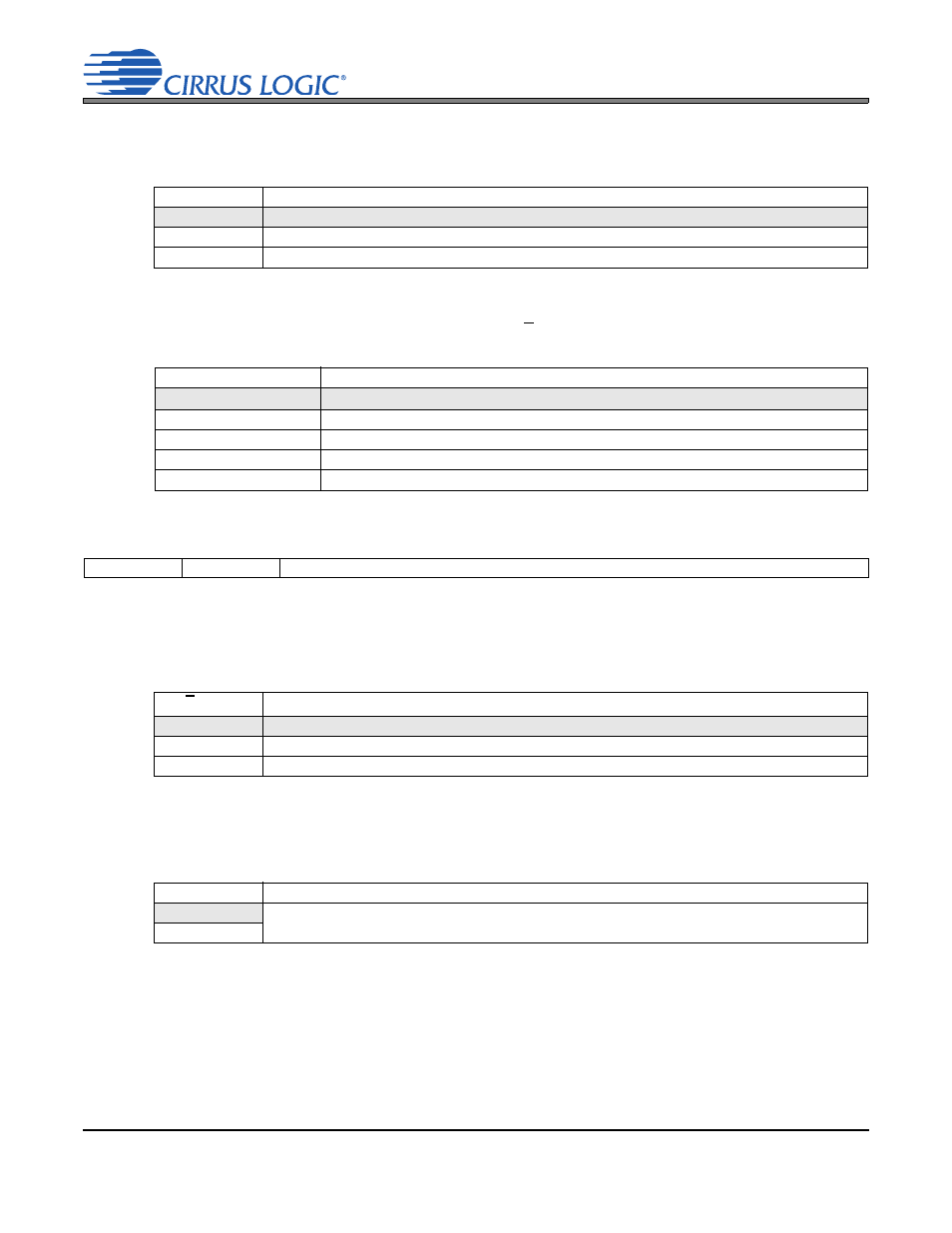

6.14.5 VSP SDIN Location

Applicable only if VSPDIF = 0b (I²S Format). Indicates if the received mono data is in the left or right por-

tion of the frame.

6.14.6 VSP SCLK Source Equals MCLK

Applicable only if VSPDIF = 0b (I²S Format) and V_M/S = 1b (Master Mode). Configures the VSP_SCLK

signal source and speed.

6.15 VSP Master Mode Clocking Control (Address 11h)

Refer to VSP Master Mode Clocking relevant control bits

“VSP SCLK Source Equals MCLK” on page 92

6.15.1 VSP Master/Slave Mode

Applicable only if VSPDIF = 0b (I²S Format). Configures the VSP clock source (direction).

6.15.2 VSP Master Mode Clock Control Dividers

Applicable only if VSPDIF = 0b (I²S Format). Provides the appropriate divide ratios for all supported serial

port master mode clock timings.

VSDIN_LOC

Position

0

Left

1

Right

Application:

Refer to section

V_SCK=MCK[1:0]

Output VSP_SCLK Sourcing Mode

00

SCLK

MCLK (SCLK = ~64

•

Fs) Mode

01

Reserved

10

SCLK = MCLK Mode

11

SCLK = Pre-MCLK Mode

Application:

Refer to section

“SCLK = MCLK Modes” on page 53

.

7

6

5

4

3

2

1

0

V_M/S

Reserved

V_MMCC5

V_MMCC4

V_MMCC3

V_MMCC2

V_MMCC1

V_MMCC0

V_M/S

Serial Port Clocks

0

Slave (Input)

1

Master (Output)

Application:

Refer to section

“Master and Slave Timing” on page 52

.

V_MMCC[5:0]

Master Mode Clock Control Settings

01 0101

Refer to section

“Serial Port Sample Rates and Master Mode Settings” on page 53

Others