11 xsp master mode clocking control (address 0dh), 1 xsp master/slave mode, 2 xsp master mode clock control dividers – Cirrus Logic CS42L73 User Manual

Page 89: 12 asp control (address 0eh), 1 tristate asp interface, P 89, Xsp master/slave mode, Cs42l73

DS882F1

89

CS42L73

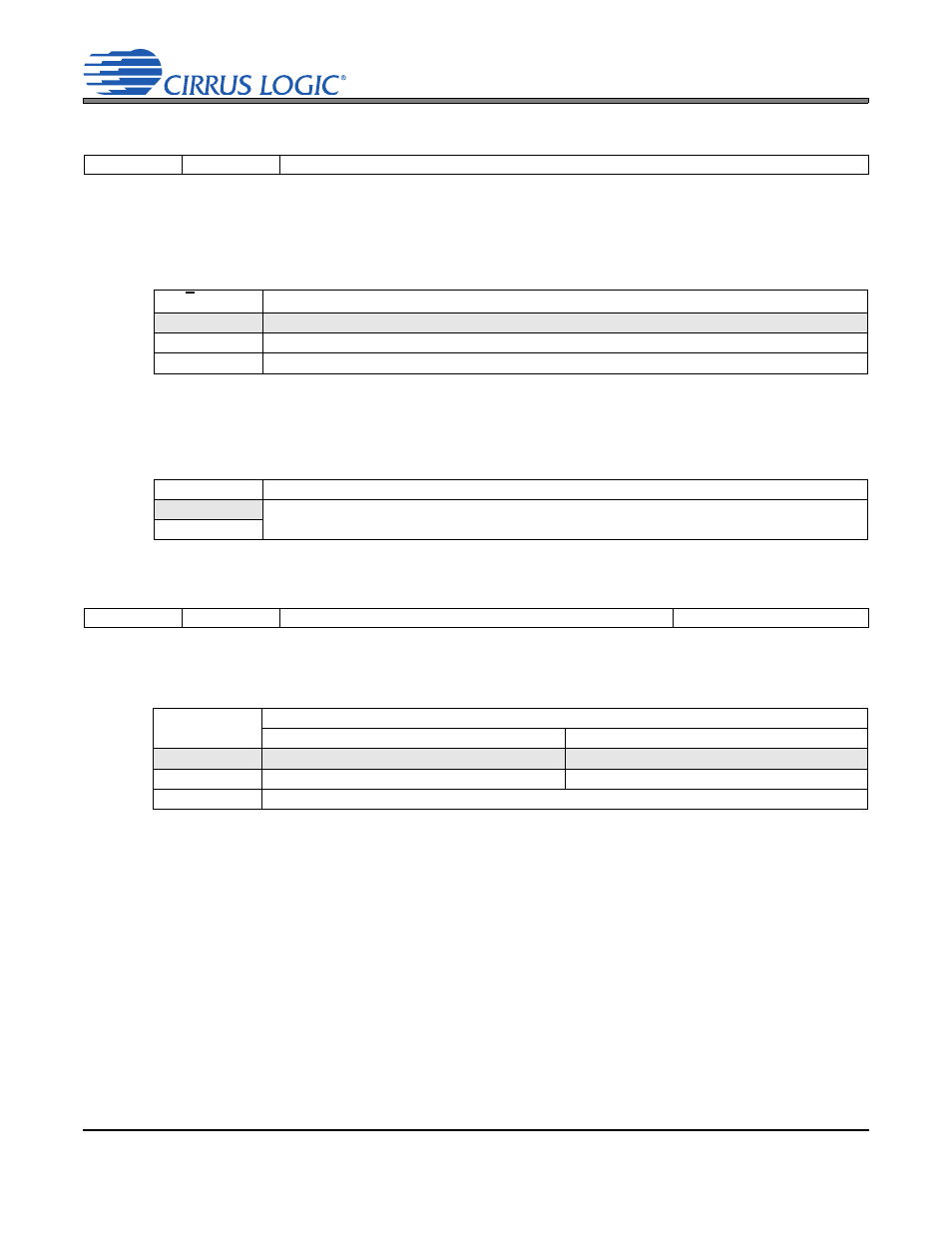

6.11 XSP Master Mode Clocking Control (Address 0Dh)

Refer to XSP Master Mode Clocking relevant control bits

“XSP SCLK Source Equals MCLK” on page 88

6.11.1 XSP Master/Slave Mode

Applicable only if XSPDIF = 0b (I²S Format). Configures the XSP clock source (direction).

6.11.2 XSP Master Mode Clock Control Dividers

Applicable only if XSPDIF = 0b (I²S Format). Provides the appropriate divide ratios for all supported serial

port master mode clock timings.

6.12 ASP Control (Address 0Eh)

6.12.1 Tristate ASP Interface

Determines the state of the ASP drivers.

Note: Slave/Master Mode is determined by the

bit described on

.

7

6

5

4

3

2

1

0

X_M/S

Reserved

X_MMCC5

X_MMCC4

X_MMCC3

X_MMCC2

X_MMCC1

X_MMCC0

X_M/S

Serial Port Clocks

0

Slave (Input)

1

Master (Output)

Application:

Refer to section

“Master and Slave Timing” on page 52

.

X_MMCC[5:0]

Master Mode Clock Control Settings

01 0101

Refer to section

“Serial Port Sample Rates and Master Mode Settings” on page 53

Others

7

6

5

4

3

2

1

0

3ST_ASP

Reserved

ASPFS3

ASPFS2

ASPFS1

ASPFS0

A_SCK=MCK1

A_SCK=MCK0

3ST_ASP

ASP State

Slave Mode

Master Mode

0

Serial port clocks are inputs and SDOUT is output

Serial port clocks and SDOUT are outputs

1

Serial port clocks are inputs and SDOUT is HI-Z

Serial port clocks and SDOUT are HI-Z

Application:

Refer to section

“High-impedance Mode” on page 52

.