9 asynchronous sample rate converters (asrcs), 10 input paths, 1 input path source selection and powering – Cirrus Logic CS42L73 User Manual

Page 59: Cs42l73

DS882F1

59

CS42L73

4.9

Asynchronous Sample Rate Converters (ASRCs)

The CS42L73 uses ASRCs to bridge potentially different sample rates at the serial ports and within the Dig-

ital Processing core. Two stereo ASRCs are used for the XSP and ASP paths, one mono ASRC is used for

the VSP input path, and three stereo ASRCs are used for the XSP, ASP, and VSP output paths. The Digital

Processing side (as opposed to the serial port side) of the ASRCs connect to the digital mixer (refer to sec-

tion

). The architecture and operation of the ASRCs is described in this section.

Multirate digital signal processing techniques are used to conceptually up-sample the incoming data to a

very high rate and then down-sample to the outgoing rate.

Internal filtering is designed so that a full input audio bandwidth of 20 kHz is preserved if the input sample

and output sample rates are greater than or equal to 44.1 kHz. When the output sample rate becomes less

than the input sample rate, the input is automatically band limited to avoid aliasing artifacts in the output

signal.

Any jitter in the incoming signal has little effect on the dynamic performance of the rate converter and has

no influence on the output clock.

A Digital PLL (DPLL) continually measures the heavily low-pass-filtered phase difference and frequency ra-

tio between input and output sample rate clocks. The DPLL, using these measures, adjusts on-the-fly the

coefficients of a linear time varying filter. This filter processes a synchronously oversampled version of the

input data. The output of this filter is then resampled to the output sample rate.

The input and output sample rate clocks are derived from the external serial port sample clock (xSP_LRCK)

and the internal Fs clock respectively in the case of the input serial ports. They are derived in the reverse

order in the case of the output serial ports.

The lock time of the ASRCs can be minimized by programming the serial port interface sample rates into

the register control words XSPFS[3:0], ASPFS[3:0], and VSPFS[3:0]. If the rates are unknown, program

these register control words to “don’t know” and incur longer lock times. Proper operation is not assured if

the sample rates are mis-programmed.

Refer to section

for additional information regarding the ASRCs.

4.10 Input Paths

4.10.1 Input Path Source Selection and Powering

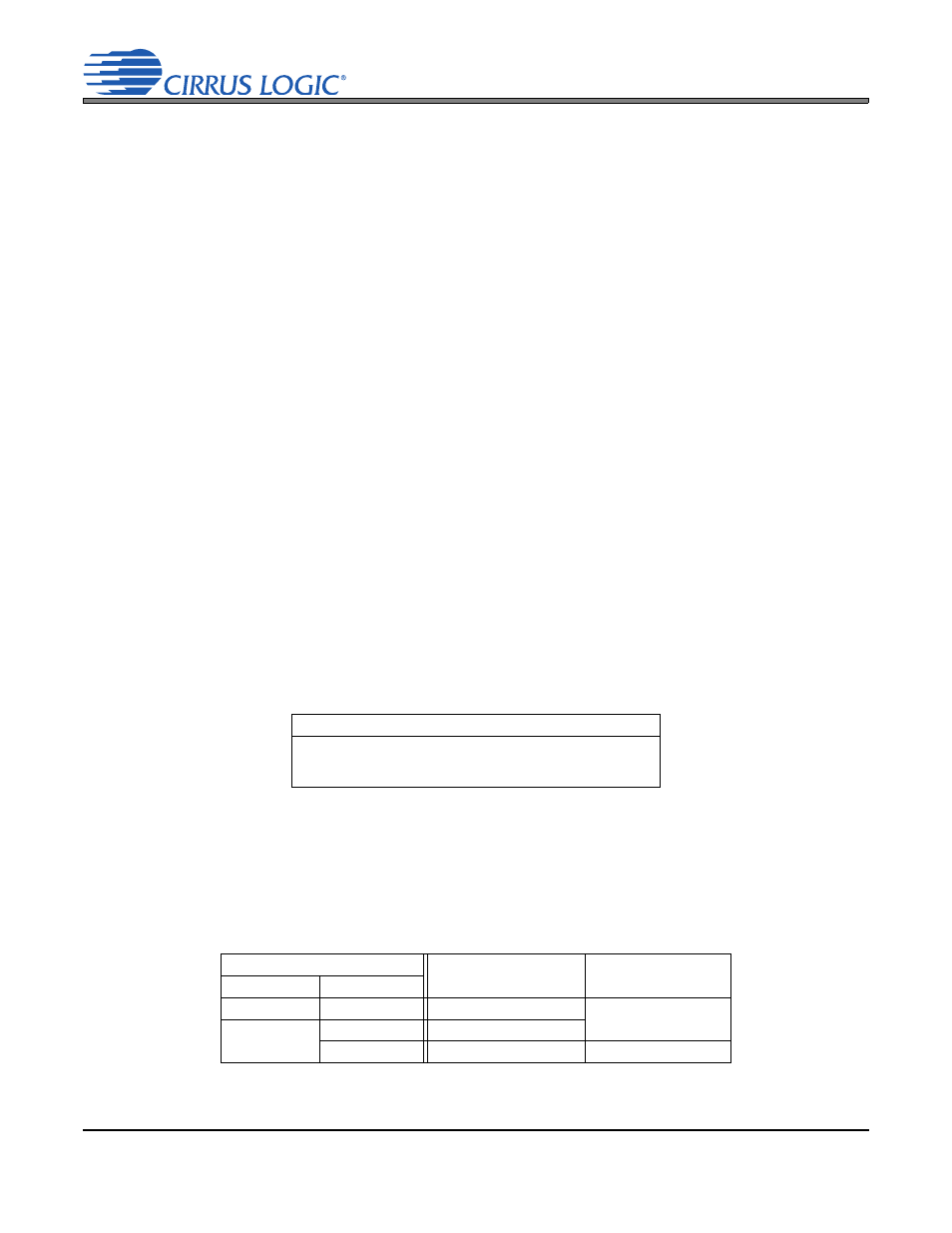

describes how the PDN_ADCx and PDN_DMICx controls affect the CS42L73 Input Path. PDN_

ADCx has priority over PDN_DMICx.

Referenced Control

Register Location

XSPFS[3:0]..........................

ASPFS[3:0]..........................

VSPFS[3:0]..........................

“XSP Sample Rate” on page 93

“ASP Sample Rate” on page 90

“VSP Sample Rate” on page 93

Table 8. Input Path Source Select and Digital Power States

Control Register States

Selected Input Path x

Data Source

Input Path x Digital

Power State

PDN_ADCx

PDN_DMICx

0

X

ADCx

On

1

0

DMICx

1

Don’t Care

Off