Cirrus Logic CDB42L51 User Manual

Cdb42l51, Evaluation board for cs42l51, Features

Copyright

© Cirrus Logic, Inc. 2007

(All Rights Reserved)

Evaluation Board for CS42L51

Features

MUXed Analog Input

– Stereo RCA Inputs

– Two Microphone Input Jacks

MUXed Analog Output

– Stereo RCA Output (w/Optional Load or

LPF)

– Stereo Headphone Jack

– Mono Speaker Driver w/Banana Posts

8 kHz to 96 kHz S/PDIF Interface

– CS8415 Digital Audio Receiver

– CS8406 Digital Audio Transmitter

I/O Stake Headers

– External Control Port Accessibility

– External DSP Serial Audio I/O Accessibility

Independent, Regulated Supplies

1.8 V to 3.3 V Logic Interface

Hardware Control

– 11 Pre-Defined Switch Settings

FlexGUI S/W Control - Windows

®

Compatible

– Pre-Defined & User-Configurable Scripts

Layout and Grounding Recommendations

Description

The CDB42L51 evaluation board is an excellent means

for evaluating the CS42L51 CODEC. Evaluation re-

quires an analog/digital signal source and analyzer, and

power supplies. Optionally, a Windows

PC-compatible

computer may be used to evaluate the CS42L51 in Soft-

ware Mode.

System timing can be provided by the CS8415, by the

CS42L51 with supplied master clock, or by an I/O stake

header with a DSP connected.

RCA phono jacks are provided for the CS42L51 analog

inputs and outputs. 1/8th inch jacks are also available

for microphone input and headphone output. Digital

data I/O is available via RCA phono or optical connec-

tors to the CS8415 and CS8406.

The Windows software provides a GUI to make config-

uration of the CDB42L51 easy. The software

communicates through the PC’s serial port to configure

the control port registers so that all features of the

CS42L51 can be evaluated. The evaluation board may

also be configured to accept external timing and data

signals for operation in a user application during system

development.

ORDERING INFORMATION

CDB42L51

Evaluation Board

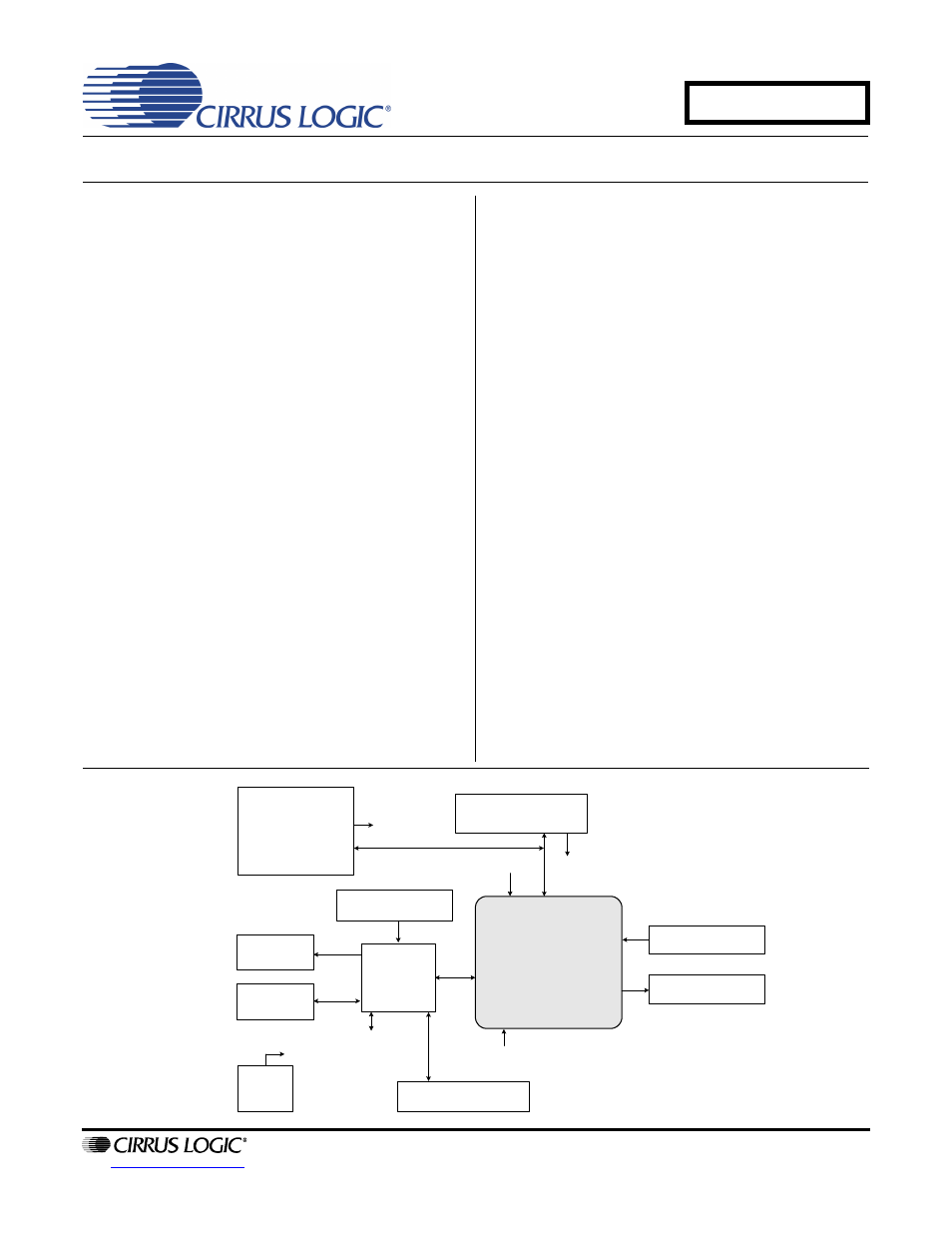

Analog Output

(Line + Headphone)

Analog Input

(Line + MIC)

Software Mode

Control Port

CS42L51

S/PDIF Input

(CS8415)

S/PDIF Output

(CS8406)

Clocks/Data Header

I²C/SPI Header

FPGA

Oscillator

(socket)

Reset

MCLK

Reset

Reset

MCLK

Reset

Hardware Mode

Switches

OCTOBER '07

DS679DB2

CDB42L51

Document Outline

- 1. System Overview

- 2. Software Mode Control

- 3. Hardware Mode Control

- 4. System Connections and Jumpers

- 5. CDB42L51 Block Diagram

- 6. CDB42L51 Schematics

- 7. CDB42L51 Layout

- 8. Errata

- 9. Revision History