Table 4-3: normal operation registers – PNI SENtral MandM User Manual

Page 18

PNI Sensor Corporation

Doc #1020129 revE

SENtral M&M Technical Datasheet

Page 17

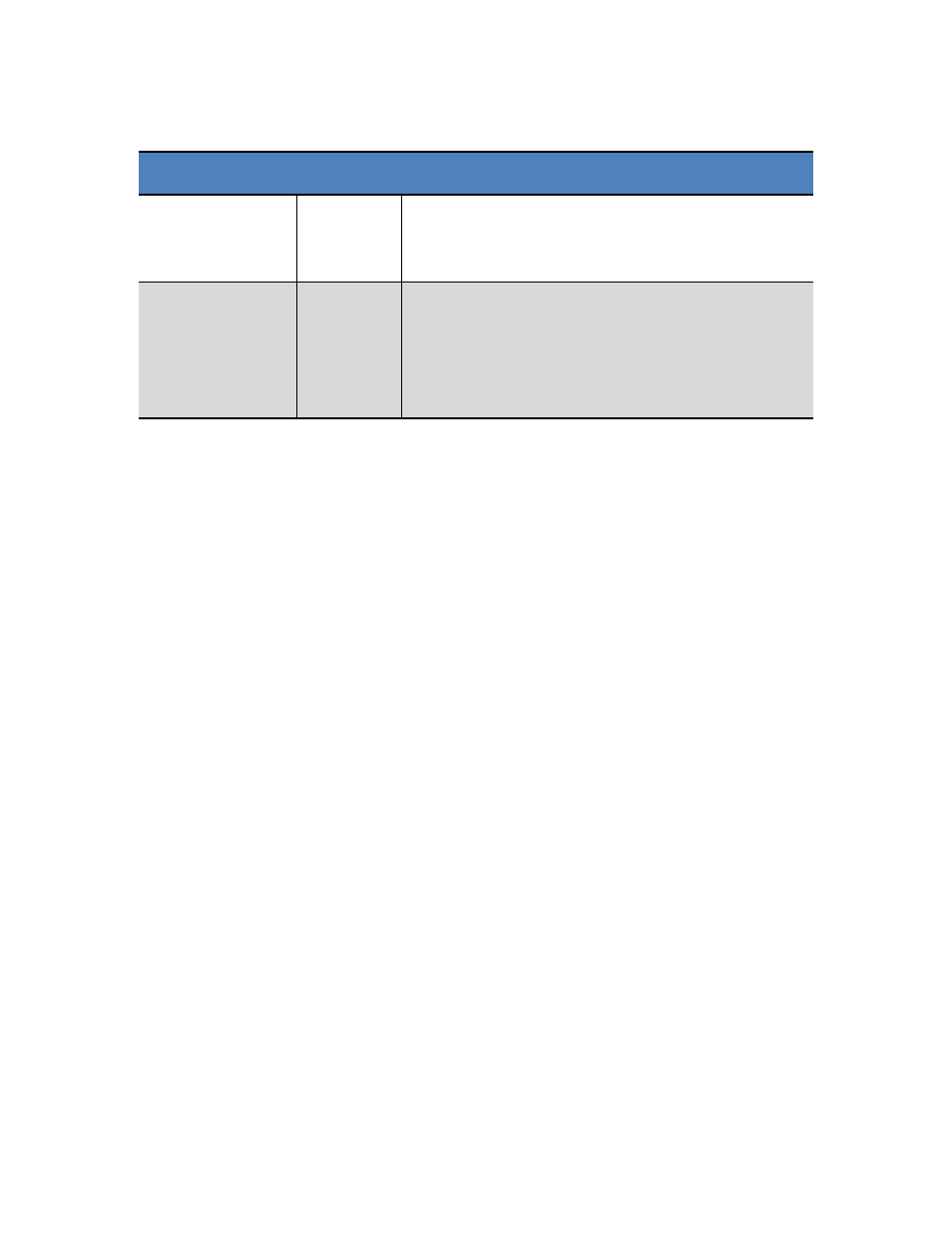

Table 4-3: Normal Operation Registers

Register Name

Address

Register Value

HostControl

0x34

[0] 1 = RunEnable

0 = Enable Initialized State (Standby State generally

is preferred since enabling Initialized State resets the

SENtral algorithm, including calibration data.)

EventStatus

0x35

‘1’ indicates a new event has been generated.

[0] CPUReset

[1] Error

[2] QuaternionResult

[3] MagResult

[4] AccelResult

[5] GyroResult

Below are the steps to follow when operating in Normal Operation state.

a) Write 0x01 to the HostControl register. This sets the RunEnable bit to ‘1’ and

enables the sensors and the SENtral algorithm.

b) If operating in an interrupt-driven mode, then the host waits until it receives an

interrupt signal from SENtral. Alternatively the host may operate on a polling basis,

rather than an interrupt-driven basis, in which case the interrupt line may not be used.

c) Once an interrupt is received by the host or the host otherwise decides to read new

data, read the EventStatus register.

d) Interpret and act on the EventStatus register in the priority shown in Figure 4-3. If bit

[1], the Error bit, is ‘1’, see Section 4.3.1. If bits [2], [3], [4], or [5], the Results bits,

are ‘1’, see Section 4.3.2. Bit [0], the CPUReset bit, should never be ‘1’, since this

bit only can be ‘1’ after a Reset or powering up and prior to loading the Configuration

File, and on the SENtral M&M module loading of the Configuration File is

automatically performed after powering up.

e) Repeat steps c and d until new orientation data is not needed and/or the host decides

to enter a different state.

Reading the EventStatus register clears it. It is possible for more than one bit position to

be ‘1’ in the EventStatus register, especially if the host does not always read the EventStatus

register after receiving an interrupt. Similarly, if multiple bits are set to ‘1’ in the

EventStatus register, once the register is read all the bits will be set to ‘0’. For this reason the

EventStatus register should be processed in the priority shown in Figure 4-3, as information

will be cleared for events that are not handled.