Questionable status, Operation status, Standard event status registers – GW Instek GOM-802 Programming Manual User Manual

Page 24: Status byte register

DC MILLI-OHM METER

PROGRAMMER MANUAL

⎯ 46 ⎯

Temperature Overload

Not Used

Not Used

Limit Test Fail HI

Limit Test Fail LO

Not Used

Ohm Overload

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

QUEStionable Status

0

1

2

3

9

15

14

13

12

11

10

8

7

6

5

4

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

OPERation Status

Not Used

2

3

0

1

14

13

12

11

10

9

8

7

6

5

4

15

Command Error

Power On

User

Request

Execution Error

Device Dependent

Error

Query Error

Not Used

Standard Event Status Registers

Operation Complete

ESB

RQS/MSS

MA

V

Not Used

Status Byte Register

Not Used

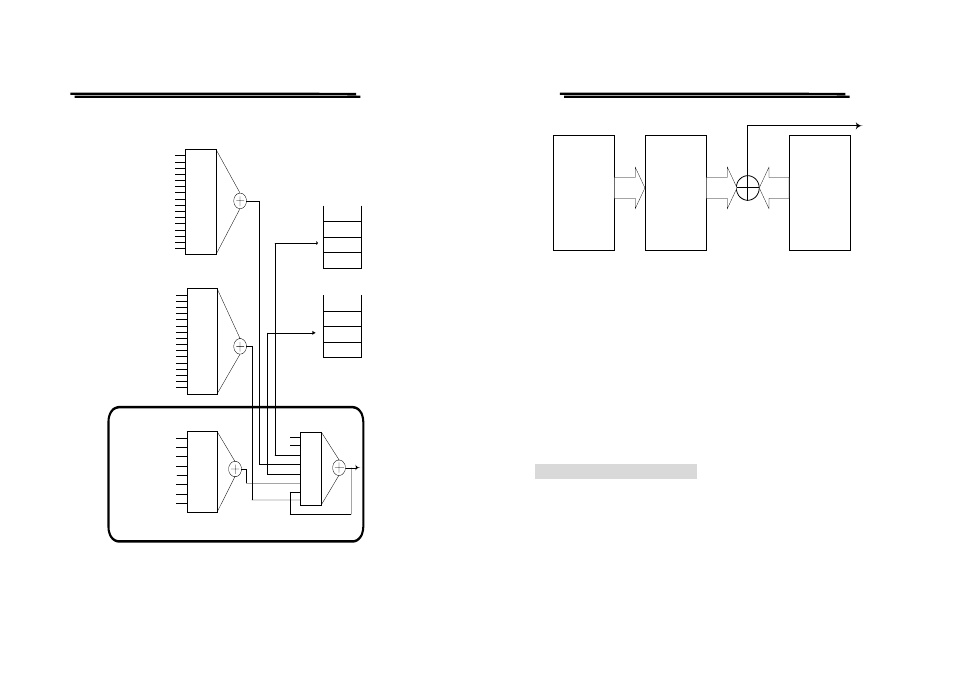

Summary of IEEE 488.2 Status Structure Registers

2

3

0

1

7

6

5

4

2

3

0

1

7

6

5

4

E/E

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

QUES

OPER

SRQ

Error/Event Queue

Output Queue

Figure 7. A graphic representation of the status registers and their connections.

DC MILLI-OHM METER

PROGRAMMER MANUAL

⎯ 47 ⎯

Figure 8: Status registers and related commands

The CONDition register is a read-only register which monitors the

present state of the instrument. The CONDition register updates in real

time and the inputs are not latched or buffered. When a condition

monitored by the CONDition register becomes true, the bit for that

condition also becomes true (1). When the condition is false, the bit is 0.

The read-only EVENt register latches any false-to-true change in

condition. Once the bit in the EVENt register is set, it is no longer

affected by changes in the corresponding bit of the CONDition register.

The bit remains set until the controller reads it. The command *CLS

(Clear Status) clears the EVENt register.

QUEStionable Status Registers.

Table 4 shows the bit designations of the 16 bit QUEStionable Status

Register.

Enable

Register

Event

Register

Condition

Register

To SBR