Thp, ck half pulse width, Tqhs, dq hold skew factor, Tqh, dq/dqs output hold time from dqs – Teledyne LeCroy QPHY-DDR2 User Manual

Page 41: Tdqsck, dqs output access time from ck/ck, Tac, dq output access time from ck/ck, Qphy-ddr2 software option

QPHY-DDR2 Software Option

QPHY-DDR2-OM-E Rev

A

41

tHP, CK half pulse width

Prerequisite: needs result of tCL and tCH Clock Tests.

tHP refers to the smaller of the actual clock LOW time and the actual clock HIGH time as provided to the device

(i.e. this value can be greater than the minimum specification limits for tCL and tCH). tHP is the minimum of the

absolute half period of the actual input clock.

tHP is an input parameter but not an input specification parameter, hence no limits are applied, it is reported as

informational only. It is used in conjunction with tQHS to derive the DRAM output timing tQH.

tHP = Min ( tCH(abs), tCL(abs) )

where,

tCH(abs) is the minimum of the actual instantaneous clock HIGH time;

tCL(abs) is the minimum of the actual instantaneous clock LOW time;

tQHS, DQ hold skew factor

This measures the sum of CK at VREF to DQS at VREF and DQ at VIH(dc) or VIL(dc) to DQS at VREF

tQH, DQ/DQS Output Hold Time From DQS

This measures the timing from DQS at VREF to DQ at VIH(dc) (rising edge) or VIL(dc) (falling edge).

Prerequisite: tHP to compute limit.

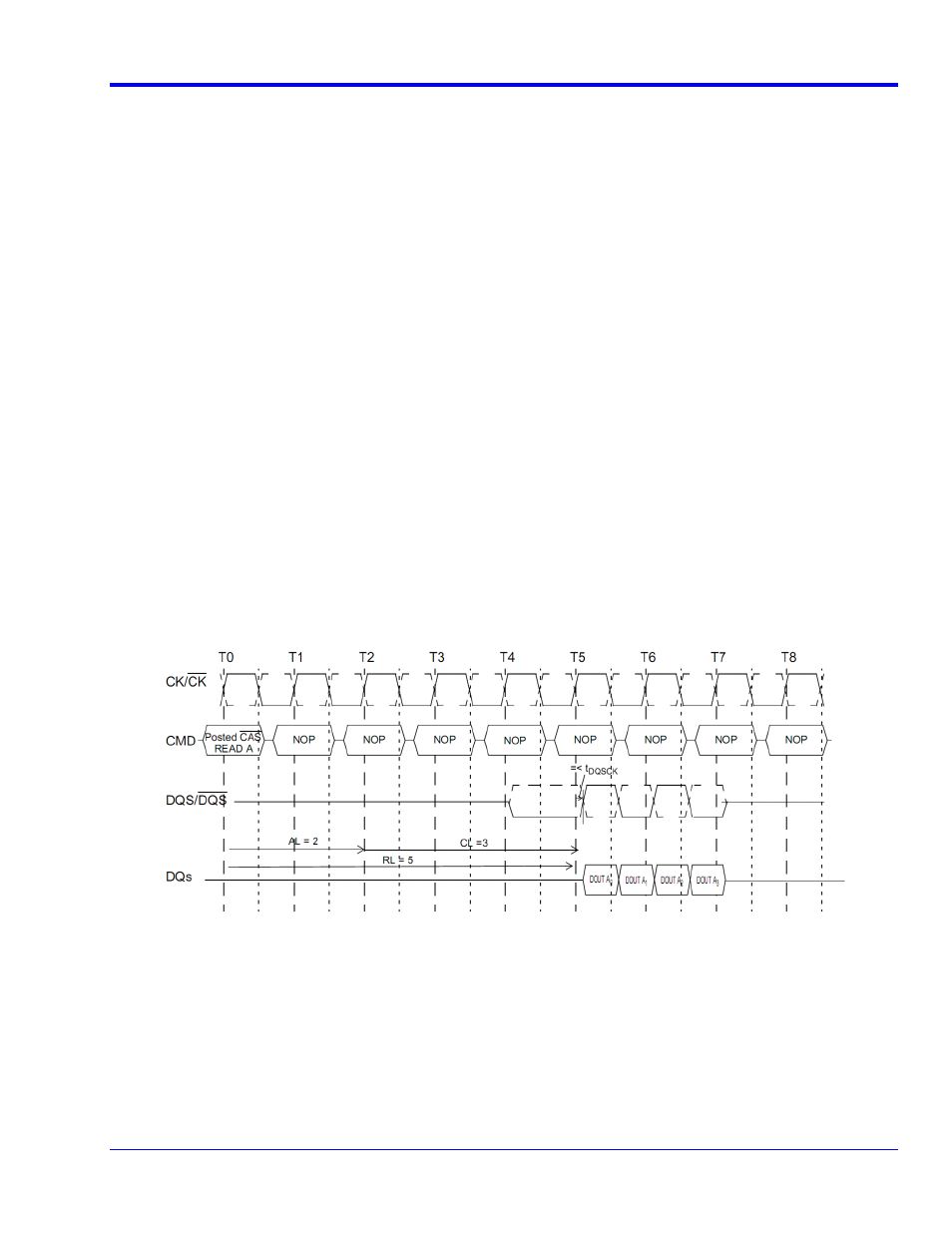

tDQSCK, DQS Output Access Time from CK/CK #

Time from CK at VREF level to DQS at VREF level.

Figure 25. Burst read operation [JESD79-2E figure 33]

This is a measure similar to tDQSS but on the Read frame and on both edges (the result can be negative).

Prerequisite: tERR(6-10per), a derating factor is applied to the limit depending on the clock jitter. This is

applicable to 667 and 800 MHz device only for both of the following tests.

tAC, DQ Output Access Time from CK/CK#

Time from CK at VREF level to DQ at VIH(ac) or VIL(ac) level.