Mainframe specifications, Continued) – Atec Agilent-83491A-92A User Manual

Page 9

9

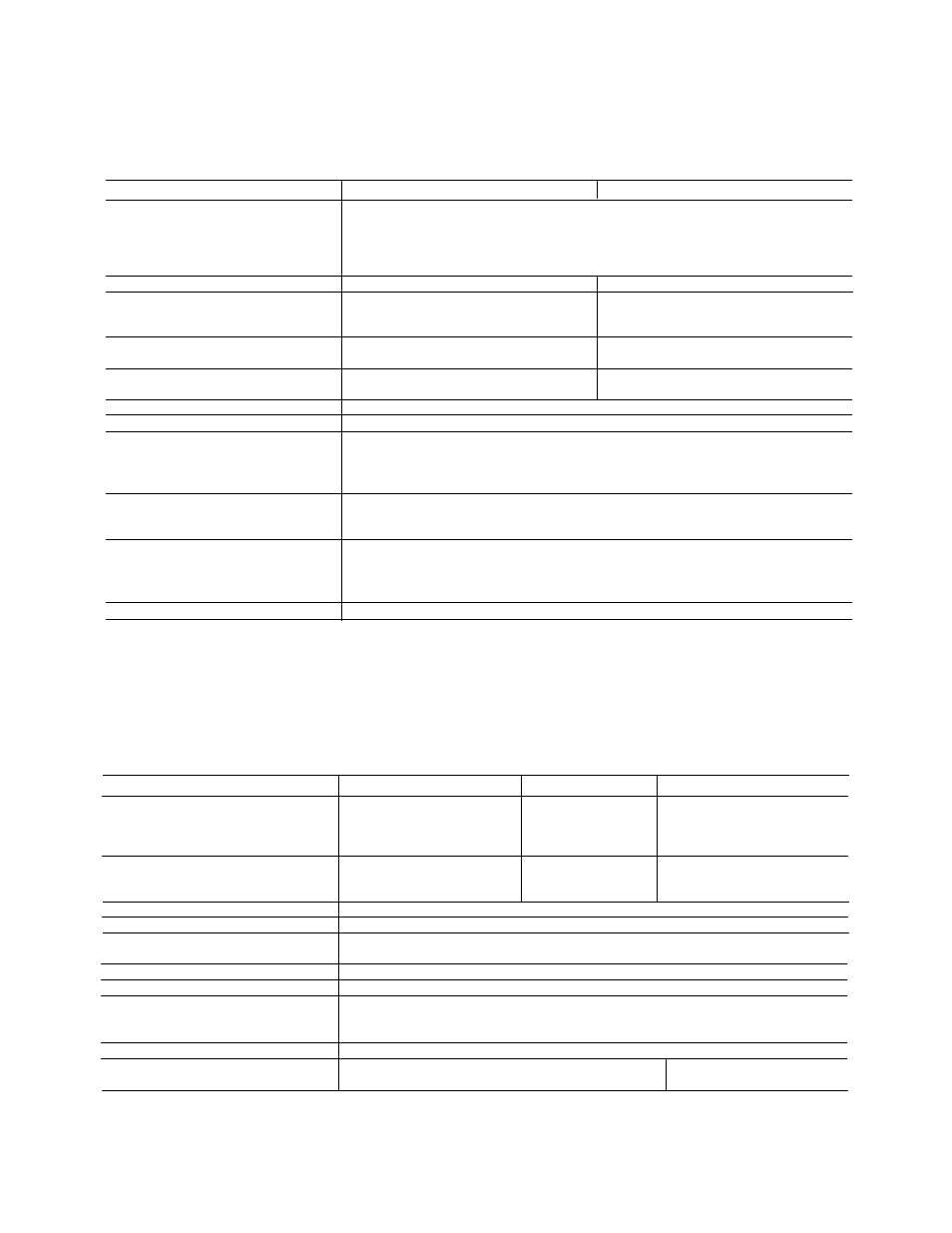

Mainframe Specifications

(continued)

Standard (Direct Trigger)

Option 001 (Divided Trigger)

Trigger Modes

Internal Trigger

1

Freerun

External Direct Trigger

2

Limited Bandwidth

3

DC to 100 MHz

Full Bandwidth

DC to 2.75 GHz

External Divided Trigger

2 to 12 GHz (1 to 15 GHz)

Jitter

Characteristic

<1.0 ps RMS + 5*10E-5 of delay setting

4

1.2 ps RMS for time delays less than 100 ns

Maximum

1.5 ps RMS + 5*10E-5 of delay setting

4

1.7 ps RMS for time delays less than 100 ns

Trigger Sensitivity

200 m Vpp (sinusoidal input or

200 m Vpp sinusoidal input from 2 to 12 GHz

200 ps minimum pulse width)

Trigger Configuration

Trigger Level Adjustment

–1 V to + 1 V

AC coupled

Edge Select

Positive or negative

Hysteresis

5

Normal or high sensitivity

Trigger Gating

Gating Input Levels

Disable: 0 to 0.6 V

(TTL compatible)

Enable: 3.5 to 5 V

Pulse width >500 ns, period >1 µs

Gating Delay

Disable: 627 ns + trigger period +

Max time displayed

Enable: 100 ns

Trigger Impedance

Nominal Impedance

50Ω

Reflection

10% for 100 ps rise time

Connector Type

3.5 mm (male)

Maximum Trigger Signal

±2 V + 2 Vac peak (+16 dBm)

Precision Time Base 86107A

86107A option 010

86107A option 020

86107A option 040

Trigger Bandwidth

2.4 – 4.0 GHz

9.0 – 12.6 GHz

9.0 – 12.6 GHz

9.0 – 12.6 GHz

18.0 – 25.0 GHz

18.0 – 25.0 GHz

39.0 – 43.0 GHz

Typical Jitter (RMS)

2.4 – 4.0 GHz trigger: <280 fs

<200 fs

9 – 12.6 GHz, 18 – 25 GHz

trigger bands: <250 fs

9 – 12.6 GHz trigger: <200 fs

38 – 45 GHz trigger: <200 fs

Time Base Linearity Error

< 100 fs

Input Signal Type

Synchronous clock, no constraint on waveform shape.

Input Signal Level

0.5 – 1.0 Vpp

1

0.2 – 1.5 Vpp (Typical functional performance)

DC Offset Range

±200 mV

Required Trigger Signal-to-Noise Ratio

≥ 200 : 1

Trigger Gating

Disable: 0 to 0.6 V

Gating Input Levels (TTL compatible)

Enable: 3.5 to 5 V

Pulse width >500 ns, period >1 µs

Trigger Impedance

50 Ω

Connector Type

3.5 mm (male)

3.5 mm (male)

2.4 mm (male)

1 To achieve characteristic performance:

Requires 86100A or B with 86100A software revision 3.0 or above.

For the 86107A with option 020, the Agilent 11742A (DC Block) is recommended if the DC offset magnitude is greater than 200 mV.

1 The freerun trigger mode internally generates an asynchronous trigger that allows viewing the sampled signal amplitude without an external trigger signal but provides no timing information. Freerun is useful in

troubleshooting external trigger problems.

2 The sampled input signal timing is recreated by using an externally supplied trigger signal that is synchronous with the sampled signal input.

3 The DC to 100 MHz mode is used to minimize the effect of high frequency signals or noise on a low frequency trigger signal.

4 Measured at 2.5 GHz with the triggering level adjusted for optimum trigger.

5 High Sensitivity Hysteresis Mode improves the high frequency trigger sensitivity but is not recommended when using noisy, low frequency signals that may result in false triggers without normal hysteresis enabled.