Clock recovery, Tdr system – Atec Agilent-83491A-92A User Manual

Page 18

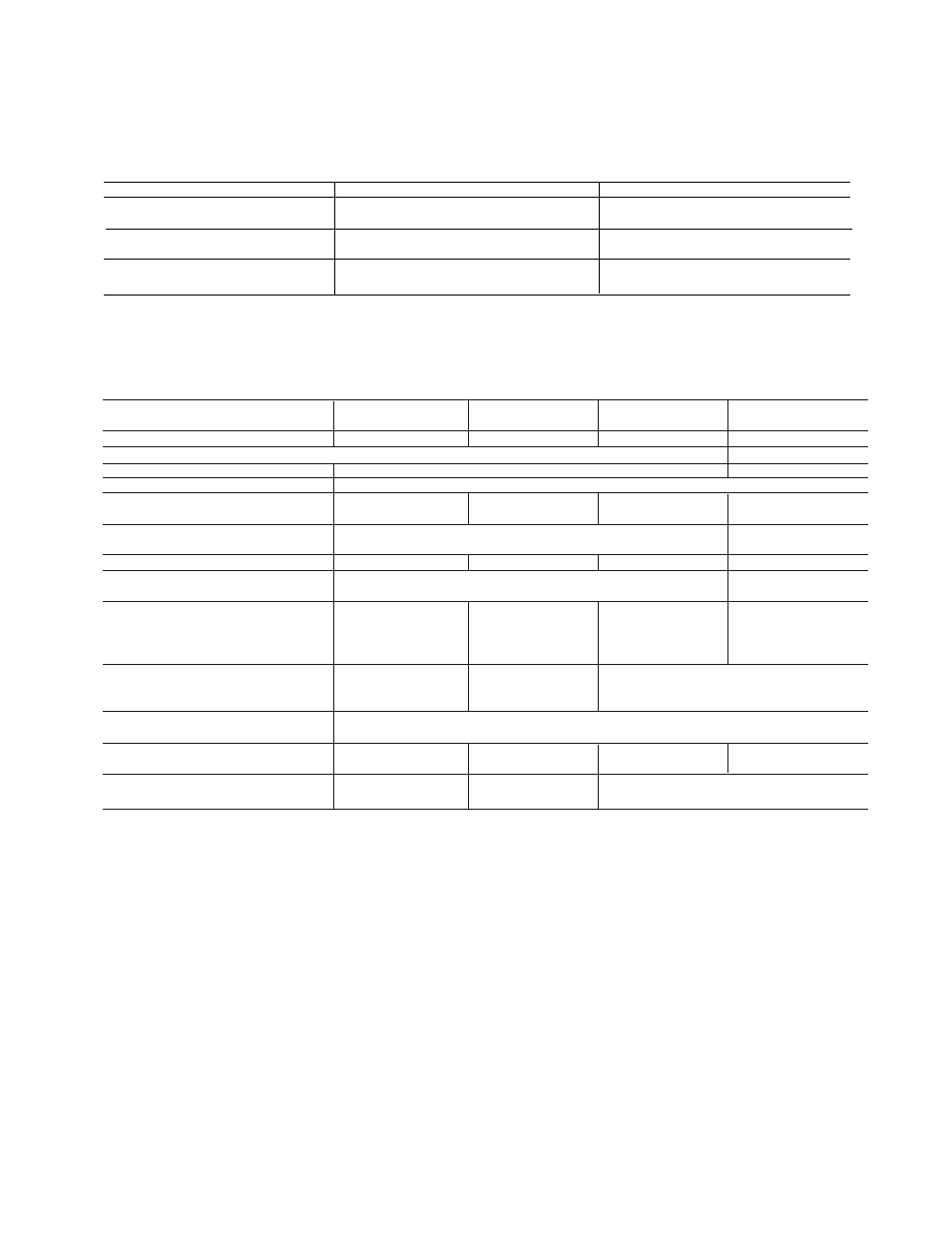

Clock Recovery Single Mode,

Multimode and Electrical Modules

83491A

83492A

83493A

83494A

Channel Type

Electrical

Multimode Optical

Single Mode Optical

Single Mode Optical

Clock Recovery Phase Locked Loop Bandwidth

Internal Path Triggering

50 to 70 kHz

90 kHz

External Output

4 MHz ±10%

Data Rates (Mb/s)

155, 622, 1063, 1250,

155, 622, 1063, 1250,

155, 622, 1250,

155, 622, 2488, 9953

2125, 2488, 2500

2125, 2488, 2500

2488, 2500

Tracking/Acquisition Range

±0.1%

155, 622, 2488, ±0.1%;

9953 ±0.03%

Internal Splitter Ratio

50/50

50/50

10/90 10/90

Output Jitter

<0.0125 UI RMS

155, 622, 2488 0.02 UI RMS

9953 0.03 UI RMS

Input Power for Clock Recovery

–10 dBm to +3 dBm

750 to 860 nm,

–20 dBm to +3 dBm

–12 dBm to +3 dBm

–10 to +3 dBm

(155, 622, 2488 Mb/s)

1000 to 1600 nm,

–8 dBm to +3 dBm

–13 to +3 dBm

(9953 Mb/s)

Input/Output Connectors

APC 3.5 mm, 50 ohm

FC/PC, 62.5/125 µm

FC/PC, 9 /125 µm

multimode, user

selectable connector

Auxiliary Recovered Clock and

Regenerated Data Outputs

Type N with SMA adapters

Input Return Loss

DC–1250 MHz, 20 dB

20 dB

28 dB

28 dB

1250–2500 MHz, 15 dB

Input Insertion Loss

DC–1250 MHz, 7 dB

5 dB Maximum

1.5 dB Maximum

1250–2500 MHz, 15 dB

18

Clock Recovery

TDR System

Oscilloscope/TDR Performance

Normalized Characteristics

Rise Time

40 ps nominal

Adjustable from larger of 10 ps or 0.08 x time/div

Maximum: 5 x time/div

TDR Step Flatness

≤ ±1% after 1 ns from edge

≤0.1%

≤ ±5%, –3% 1 ns from edge

Low Level

0.00 V ±2 mV

0.00 V ±2 mV

High Level

±200 mV ± 2 mV

±200 mV ± 2 mV

TDR System