Zxld1362, Device description – Diodes ZXLD1362 User Manual

Page 5

ZXLD1362

ZXLD1362

Document number: DS33472 Rev. 5 - 2

5 of 24

May 2012

© Diodes Incorporated

A Product Line of

Diodes Incorporated

Device Description

The device, in conjunction with the coil (L1) and current sense resistor (R

S

), forms a self-oscillating continuous-mode buck converter.

Device operation

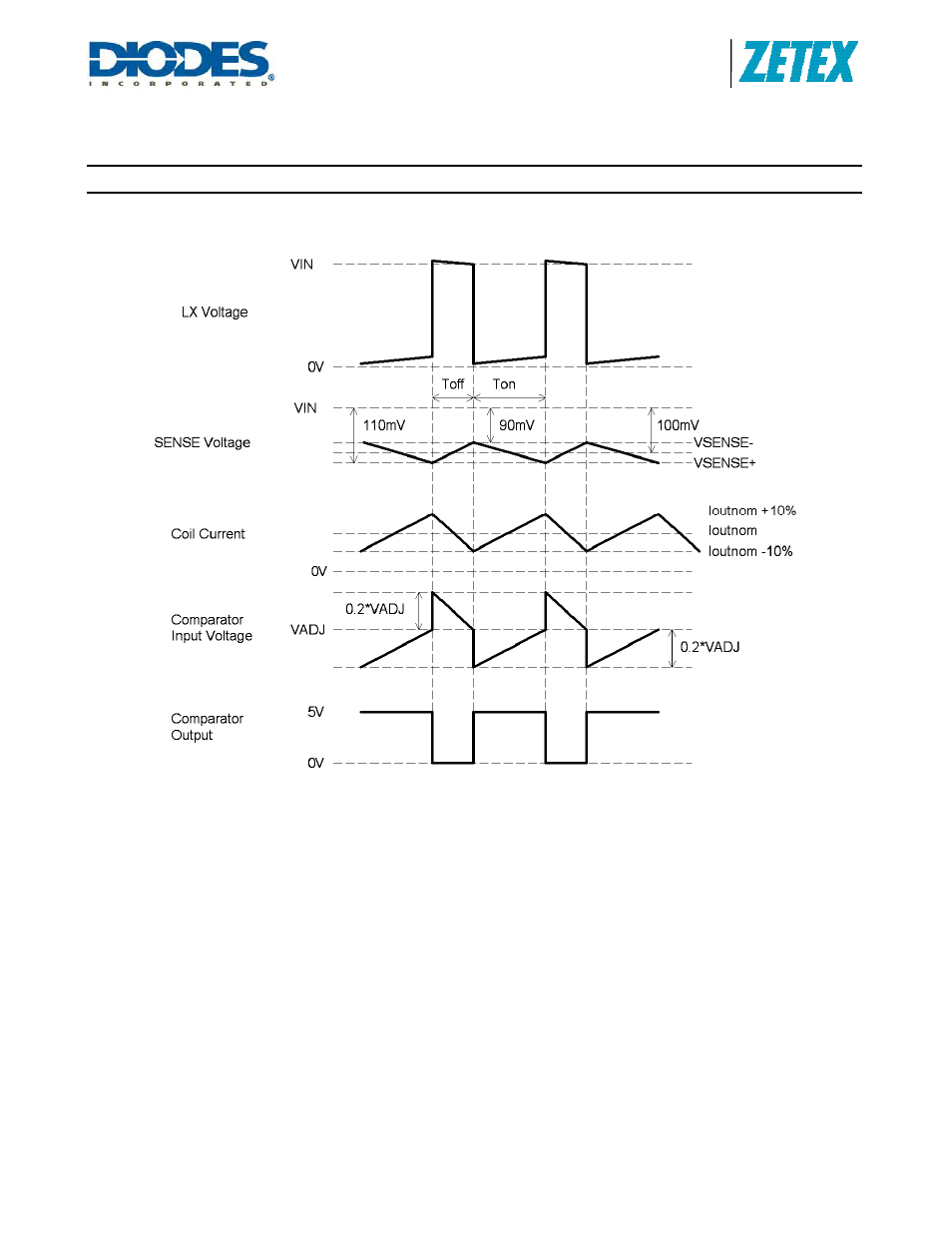

(refer to Figure 1 - Block diagram and Figure 2 Operating waveforms)

Figure 2. Theoretical Operating Waveforms

Operation can be best understood by assuming that the ADJ

pin of the device is unconnected and the voltage on this pin

(V

ADJ

) appears directly at the (+) input of the comparator.

When input voltage V

IN

is first applied, the initial current in L1

and R

S

is zero and there is no output from the current sense

circuit. Under this condition, the (-) input to the comparator is at

ground and its output is high. This turns MN on and switches

the LX pin low, causing current to flow from V

IN

to ground, via

R

S

, L1 and the LED(s). The current rises at a rate determined

by V

IN

and L1 to produce a voltage ramp (V

SENSE

) across R

S

.

The supply referred voltage V

SENSE

is forced across internal

resistor R1 by the current sense circuit and produces a

proportional current in internal resistors R2 and R3. This

produces a ground referred rising voltage at the (-) input of the

comparator. When this reaches the threshold voltage (V

ADJ

),

the comparator output switches low and MN turns off. The

comparator output also drives another NMOS switch, which

bypasses internal resistor R3 to provide a controlled amount of

hysteresis. The hysteresis is set by R3 to be nominally 10% of

V

ADJ

.

When MN is off, the current in L1 continues to flow via D1 and

the LED(s) back to V

IN

. The current decays at a rate

determined by the LED(s) and diode forward voltages to

produce a falling voltage at the input of the comparator. When

this voltage returns to V

ADJ

, the comparator output switches

high again. This cycle of events repeats, with the comparator

input ramping between limits of V

ADJ

± 10%.