Rainbow Electronics AT17LV040 User Manual

Features, Description

1

Features

•

EE Programmable 65,536 x 1-, 131,072 x 1-, 262,144 x 1-, 524,288 x 1-, 1,048,576 x 1-,

2,097,152 x 1-, and 4,194,304 x 1-bit Serial Memories Designed to Store Configuration

Programs for Field Programmable Gate Arrays (FPGAs)

•

Available as a 3.3V (±10%) and 5.0V (±5% Commercial, ±10% Industrial) Version

•

In-System Programmable (ISP) via Two-Wire Bus

•

Simple Interface to SRAM FPGAs

•

Compatible with Atmel AT6000, AT40K and AT94K Devices, Altera FLEX

®

, APEX

™

Devices,

Lucent ORCA

®

FPGAs, Xilinx XC3000

™

, XC4000

™

, XC5200

™

, Spartan

®

, Virtex

®

FPGAs

•

Cascadable Read-back to Support Additional Configurations or Higher-density Arrays

•

Very Low-power CMOS EEPROM Process

•

Programmable Reset Polarity

•

Available in 6 mm x 6 mm x 1 mm 8-lead LAP (Pin-compatible with 8-lead SOIC/VOIC

Packages), 8-lead PDIP, 8-lead SOIC, 20-lead PLCC, 20-lead SOIC, 44-lead PLCC and

44-lead TQFP Packages

•

Emulation of Atmel’s AT24CXXX Serial EEPROMs

•

Low-power Standby Mode

•

High-reliability

– Endurance: 100,000 Write Cycles

– Data Retention: 90 Years for Industrial Parts (at 85

°

C) and 190 Years for

Commercial Parts (at 70

°

C)

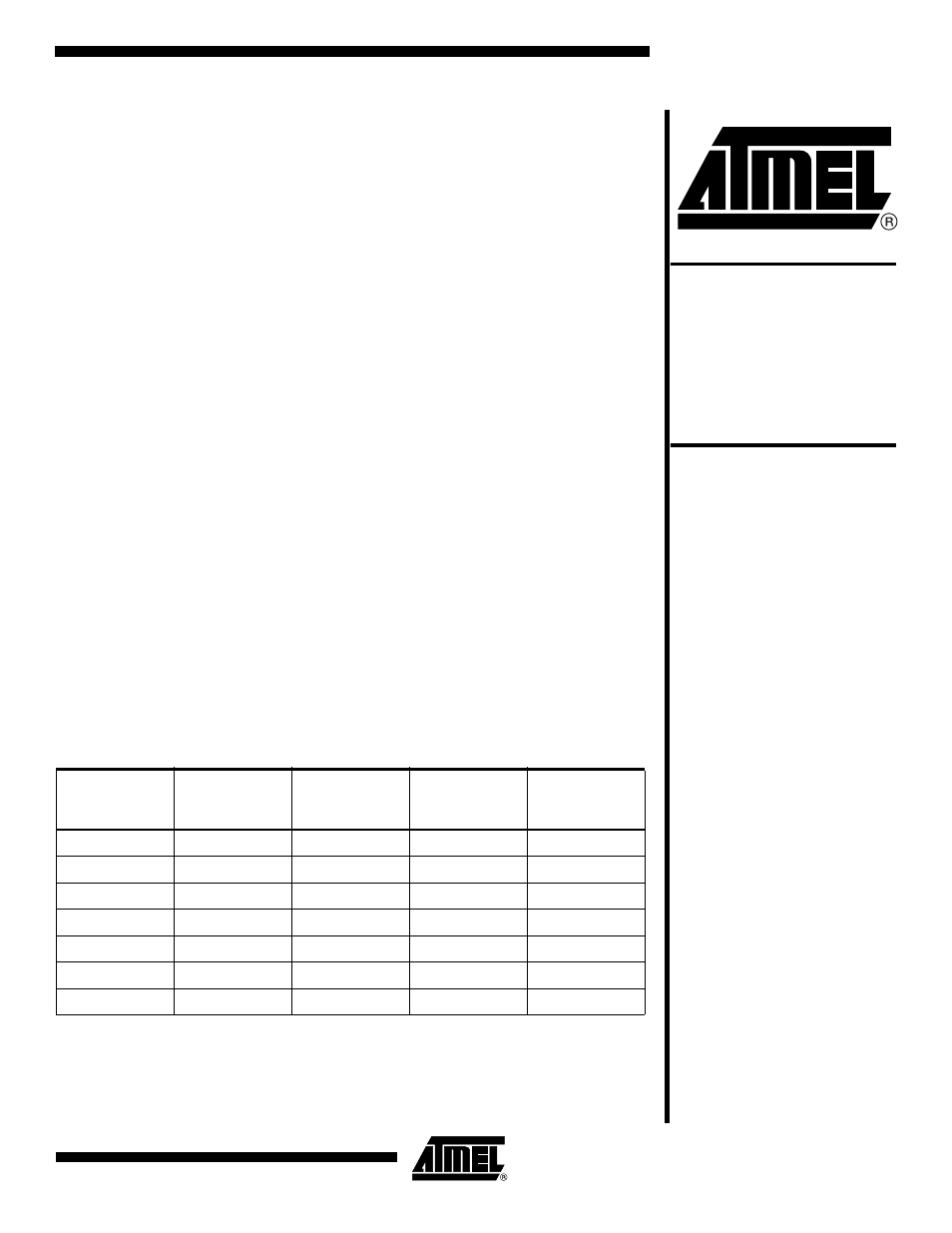

Description

The AT17LV series FPGA Configuration EEPROMs (Configurators) provide an easy-

to-use, cost-effective configuration memory for Field Programmable Gate Arrays. The

AT17LV series device is packaged in the 8-lead LAP, 8-lead PDIP, 8-lead SOIC, 20-

lead PLCC, 20-lead SOIC, 44-lead PLCC and 44-lead TQFP, see Table 1. The

AT17LV series Configurators uses a simple serial-access procedure to configure one

or more FPGA devices. The user can select the polarity of the reset function by pro-

gramming four EEPROM bytes. These devices also support a write-protection

mechanism within its programming mode.

The AT17LV series configurators can be programmed with industry-standard program-

mers, Atmel’s ATDH2200E Programming Kit or Atmel’s ATDH2225 ISP Cable.

Notes:

1. The 8-lead LAP package has the same footprint as the 8-lead SOIC. Since an 8-

lead SOIC package is not available for the AT17LV512/010/002 devices, it is possi-

ble to use an 8-lead LAP package instead.

2. The pinout for the AT17LV65/128/256 devices is not pin-for-pin compatible with the

AT17LV512/010/002 devices.

3. Refer to the AT17Fxxx datasheet, available on the Atmel web site.

Table 1. AT17LV Series Packages

Package

AT17LV65/

AT17LV128/

AT17LV256

AT17LV512/

AT17LV010

AT17LV002

AT17LV040

8-lead LAP

Yes

Yes

Yes

(3)

8-lead PDIP

Yes

Yes

–

–

8-lead SOIC

Yes

Use 8-lead LAP

(1)

Use 8-lead LAP

(1)

(3)

20-lead PLCC

Yes

Yes

Yes

–

20-lead SOIC

Yes

(2)

Yes

(2)

Yes

(2)

–

44-lead PLCC

–

–

Yes

Yes

44-lead TQFP

–

–

Yes

Yes

FPGA

Configuration

EEPROM

Memory

AT17LV65

AT17LV128

AT17LV256

AT17LV512

AT17LV010

AT17LV002

AT17LV040

3.3V and 5V

System Support

Rev. 2321D–CNFG–10/02

Document Outline

- Features

- Description

- Pin Configuration

- Block Diagram

- Device Description

- Pin Description

- FPGA Master Serial Mode Summary

- Control of Configuration

- Cascading Serial Configuration EEPROMs

- AT17LV Series Reset Polarity

- Programming Mode

- Standby Mode

- Absolute Maximum Ratings*

- Operating Conditions

- DC Characteristics

- DC Characteristics

- AC Characteristics

- AC Characteristics when Cascading

- AC Characteristics

- AC Characteristics

- Thermal Resistance Coefficients(1)

- Ordering Information

- Packaging Information