Uart control and status register b – ucsrb – Rainbow Electronics AT90LS4433 User Manual

Page 58

58

AT90S/LS4433

1042G–AVR–09/02

• Bit 4 – FE: Framing Error

This bit is set if a Framing Error condition is detected, i.e., when the stop bit of an incom-

ing character is zero.

The FE bit is cleared when the stop bit of received data is one.

• Bit 3 – OR: OverRun

This bit is set if an OverRun condition is detected, i.e., when a character already present

in the UDR Register is not read before the next character has been shifted into the

Receiver Shift Register. The OR bit is buffered, which means that it will be set once the

valid data still in UDRE is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

• Bits 2..1 – Res: Reserved Bits

These bits are reserved bits in the AT90S4433 and will always read as zero.

• Bit 0 – MPCM: Multi-processor Communication Mode

This bit is used to enter Multi-processor Communication mode. The bit is set when the

slave MCU waits for an address byte to be received. When the MCU has been

addressed, the MCU switches off the MPCM bit and starts data reception.

For a detailed description, see “Multi-processor Communication Mode”.

UART Control and Status

Register B – UCSRB

• Bit 7 – RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in UCSRA will cause the Receive

Complete Interrupt routine to be executed, provided that global interrupts are enabled.

• Bit 6 – TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in UCSRA will cause the Transmit

Complete Interrupt routine to be executed, provided that global interrupts are enabled.

• Bit 5 – UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in UCSRA will cause the UART Data

Register Empty Interrupt routine to be executed, provided that global interrupts are

enabled.

• Bit 4 – RXEN: Receiver Enable

This bit enables the UART Receiver when set (one). When the Receiver is disabled, the

RXC, OR, and FE status flags cannot become set. If these flags are set, turning off

RXEN does not cause them to be cleared.

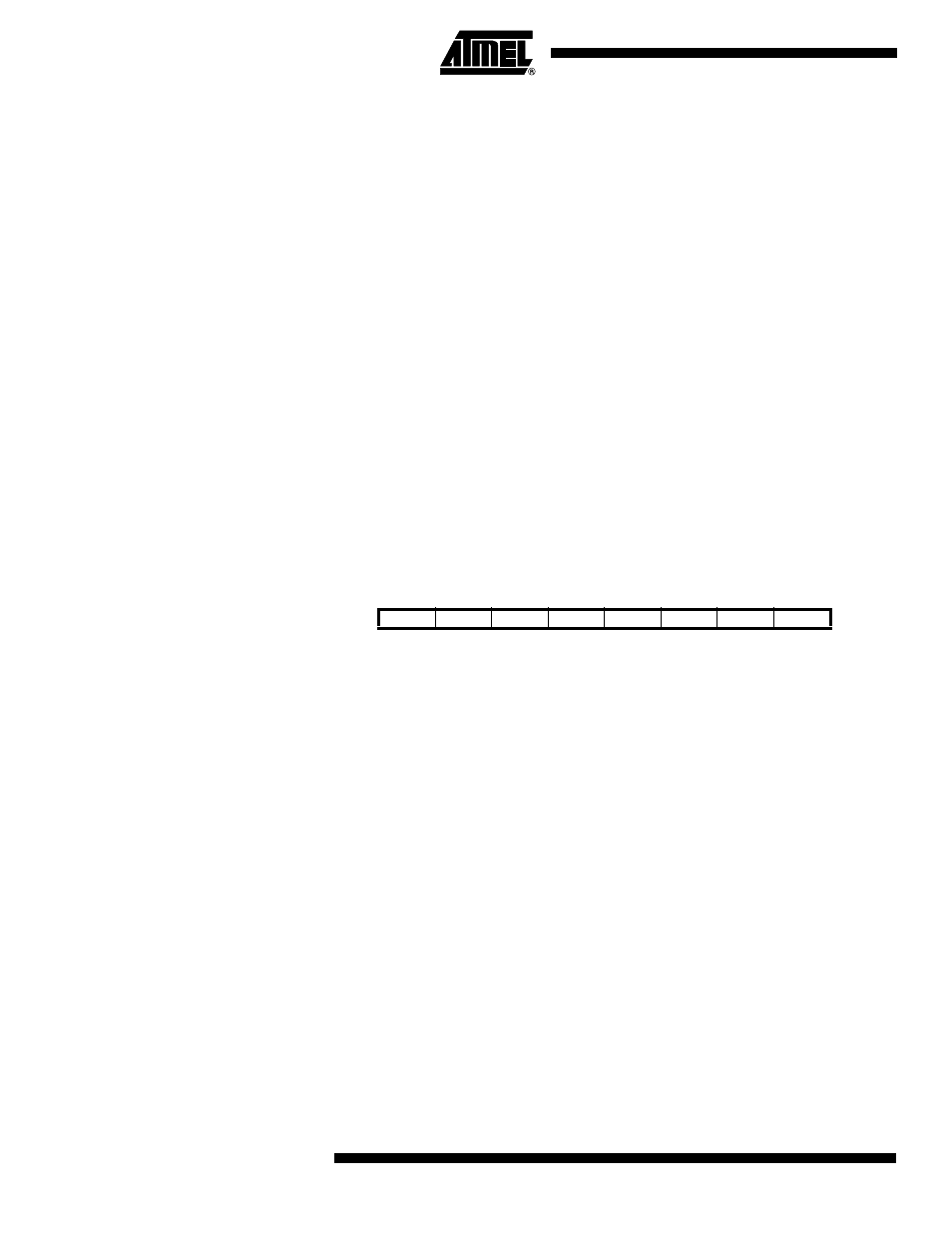

Bit

7

6

5

4

3

2

1

0

$0A ($2A)

RXCIE

TXCIE

UDRIE

RXEN

TXEN

CHR9

RXB8

TXB8

UCSRB

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R

W

Initial Value

0

0

0

0

0

0

1

0