Max6900 i, C-compatible rtc in a tdfn, Applications information – Rainbow Electronics MAX6900 User Manual

Page 5

days, including corrections for leap year up to the year

2100.

Crystal Oscillator

The MAX6900 uses an external, standard 12.5pF load

watch crystal. No other external components are

required for this timekeeping oscillator. Power-up oscil-

lator start-time is dependent mainly upon applied V

CC

and ambient temperature. The MAX6900, because of

its low timekeeping current, exhibits a typical startup

time between 5s to 10s.

I

2

C-Compatible Interface

Interfacing the MAX6900 with a microprocessor or

other I

2

C master is made easier by using the serial, I

2

C-

bus-compatible or other I

2

C master interface. Only 2

wires are required to communicate with the clock and

SRAM: SCL (serial clock) and SDA (data line). Data is

transferred to and from the MAX6900 over the I/O data

line, SDA. The MAX6900 uses 7-bit slave ID address-

ing. The MAX6900 does not respond to general call

address commands.

Applications Information

I

2

C-Bus-Compatible Interface

The I

2

C-bus-compatible serial interface allows bidirec-

tional, 2-wire communication between multiple ICs. The

two lines are SDA and SCL. Connect both lines to a

positive supply through individual pullup resistors. A

device on the I

2

C-compatible bus that generates a

message is called a transmitter and a device that

receives the message is a receiver. The device that

controls the message is the master and the devices

that are controlled by the master are called slaves

(Figure 3). The word message refers to data in the form

of three 8-bit bytes for a Single Read or Write. The first

byte is the Slave ID byte, the second byte is the

Address/Command byte, and the third is the data.

Data transfer can only be initiated when the bus is not

busy (both SDA and SCL are high). A high-to-low tran-

sition of SDA while SCL is high is defined as the Start

(S) condition; low-to-high transition of the data line

while SCL is high is defined as the Stop (P) condition

(Figure 4).

MAX6900

I

2

C-Compatible RTC in a TDFN

_______________________________________________________________________________________

5

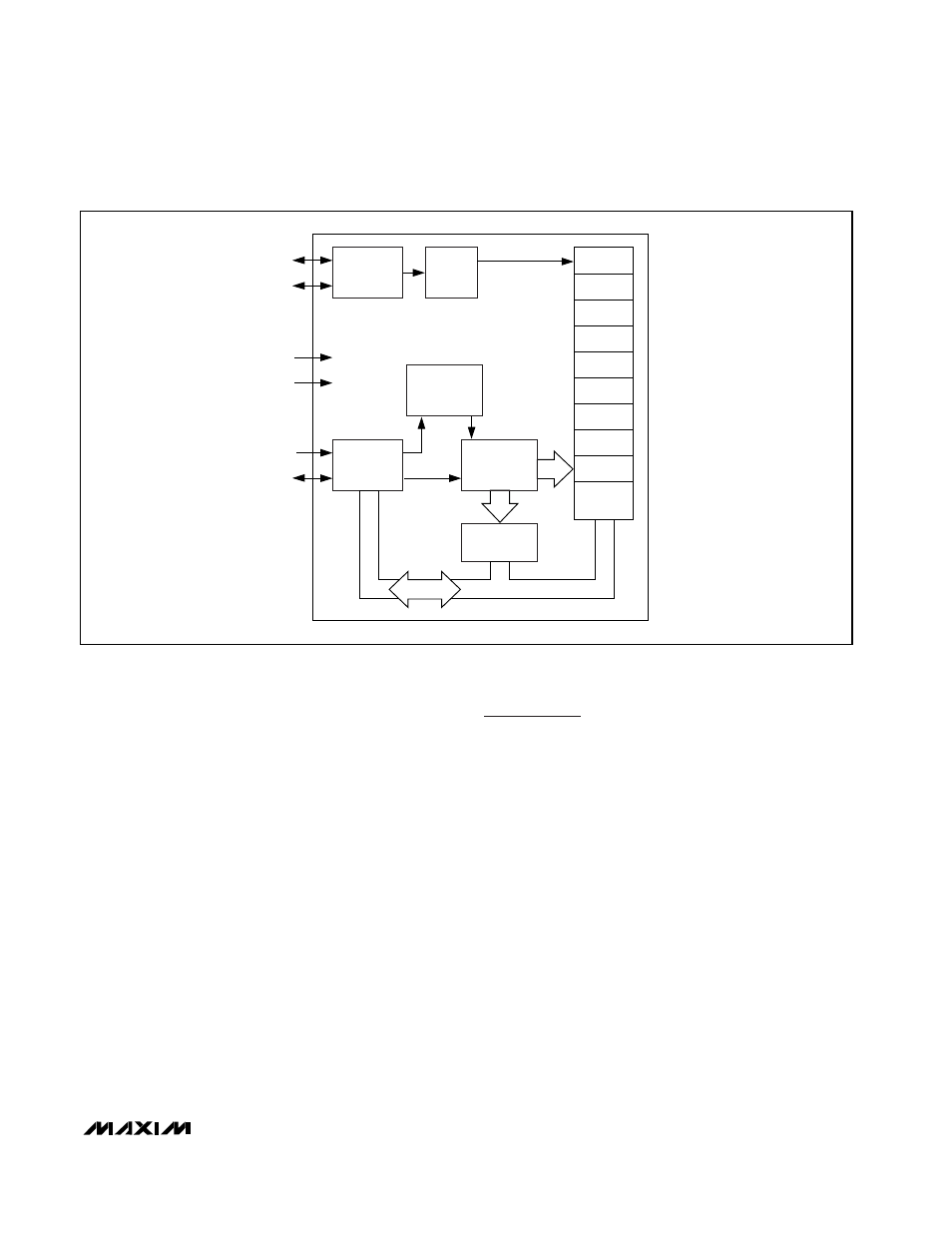

Figure 2. Functional Diagram

OSCILLATOR

32.768kHz

CONTROL

LOGIC

ADDRESS

REGISTER

31 X 8

SRAM

I

2

C BUS

INTERFACE

DIVIDER

SECONDS

MINUTES

HOURS

DATE

MONTH

DAY

YEAR

CONTROL

CENTURY

CLOCK

BURST

1Hz

X1

X2

VCC

GND

SCL

SDA