Polling circuit and control logic, Basic clock cycle of the digital circuitry, U3741bm – Rainbow Electronics U3741BM User Manual

Page 10

10

U3741BM

4662B–RKE–10/04

Polling Circuit and Control Logic

The receiver is designed to consume less than 1 mA while being sensitive to signals

from a corresponding transmitter. This is achieved via the polling circuit. This circuit

enables the signal path periodically for a short time. During this time the bit check logic

verifies the presence of a valid transmitter signal. Only if a valid signal is detected the

receiver remains active and transfers the data to the connected microcontroller. If there

is no valid signal present, the receiver is in sleep mode most of the time resulting in low

current consumption. This condition is called polling mode. A connected microcontroller

is disabled during that time.

All relevant parameters of the polling logic can be configured by the connected micro-

controller. This flexibility enables the user to meet the specifications in terms of current

consumption, system response time, data rate etc.

Regarding the number of connection wires to the microcontroller, the receiver is very

flexible. It can be either operated by a single bi-directional line to save ports to the con-

nected microcontroller, it can be operated by up to three uni-directional ports.

Basic Clock Cycle of the

Digital Circuitry

The complete timing of the digital circuitry and the analog filtering is derived from one

clock. According to Figure 7, this clock cycle T

Clk

is derived from the crystal oscillator

(XTO) in combination with a divider. The division factor is controlled by the logical state

at pin MODE. According to section “RF Front End” on page 4, the frequency of the crys-

tal oscillator (f

XTO

) is defined by the RF input signal (f

RFin

) which also defines the

operating frequency of the local oscillator (f

LO

).

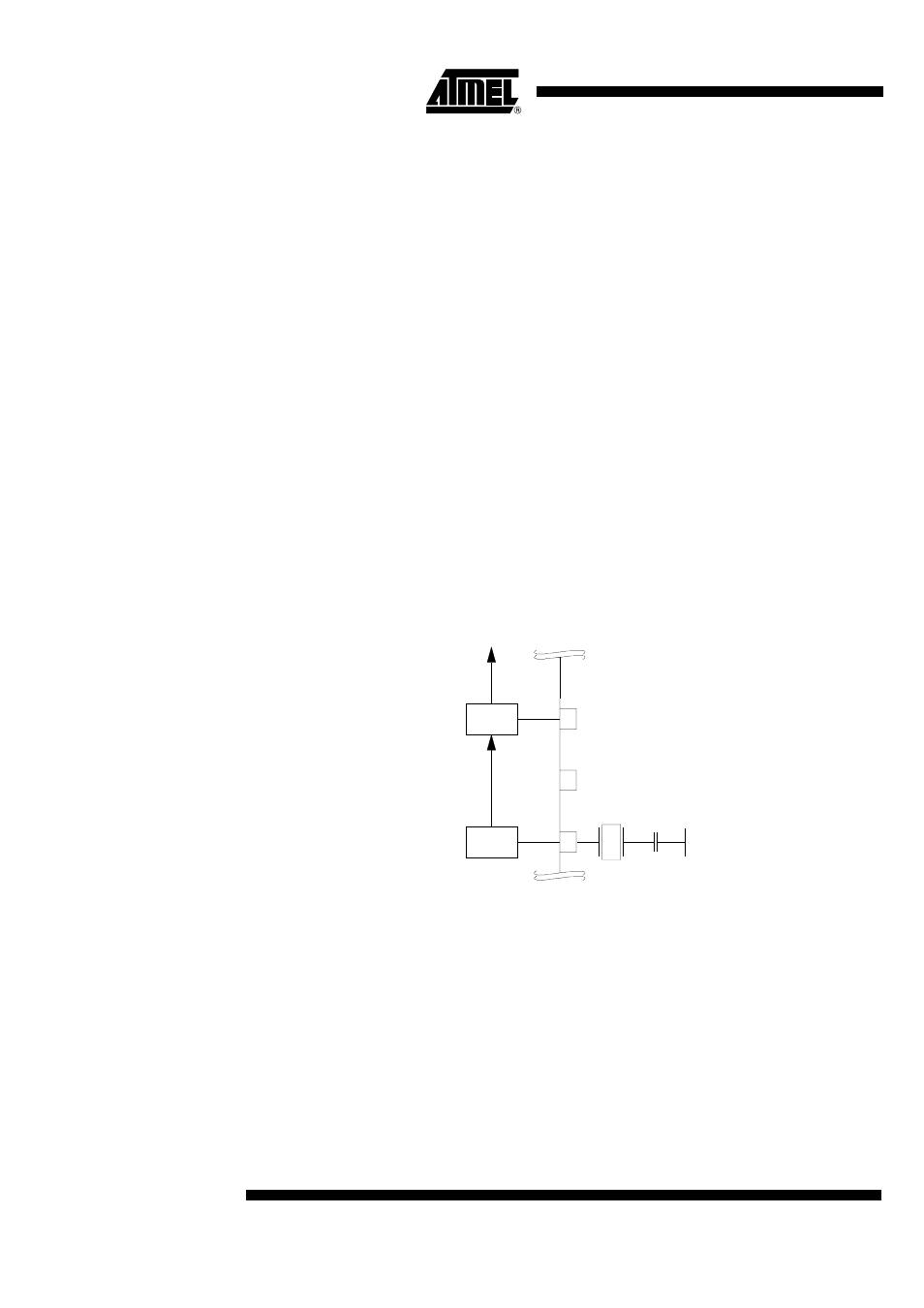

Figure 7. Generation of the Basic Clock Cycle

Pin MODE can now be set in accordance with the desired clock cycle T

Clk

. T

Clk

controls

the following application-relevant parameters:

•

Timing of the polling circuit including bit check

•

Timing of analog and digital signal processing

•

Timing of register programming

•

Frequency of the reset marker

•

F filter center frequency (f

IF0

)

Most applications are dominated by two transmission frequencies: f

Send

= 315 MHz is

mainly used in the USA, f

Send

= 433.92 MHz in Europe. In order to ease the usage of all

T

Clk

-dependent parameters, the electrical characteristics display three conditions for

each parameter.

DVCC

XTO

MODE

T

Clk

f

XTO

16

15

14

XTO

Divider

:14/:10

L : USA (:10)

H: Europe (:14)