Power management, Table 2. power management registers – Rainbow Electronics MAX98089 User Manual

Page 67

���������������������������������������������������������������� Maxim Integrated Products 67

MAX98089

Low-Power, Stereo Audio Codec

with FlexSound Technology

Power Management

The IC includes comprehensive power management to allow the disabling of all unused circuits, minimizing supply

current.

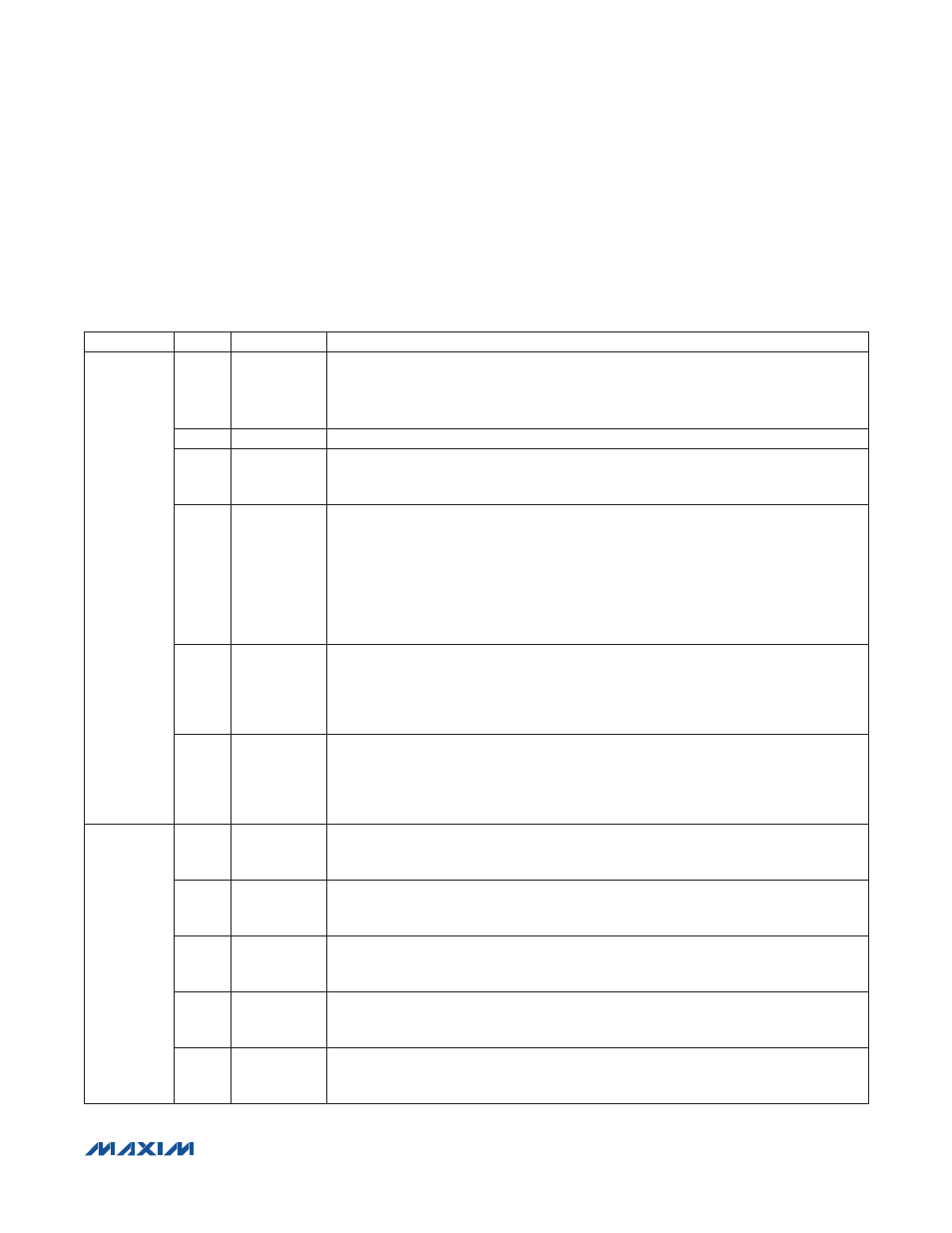

Table 2. Power Management Registers

REGISTER

BIT

NAME

DESCRIPTION

0x51

7

SHDN

Global Shutdown. Disables everything except the headset detection circuitry, which is

controlled separately.

0 = Device Shutdown

1 = Device Enabled

6

VBATEN

See the Battery Measurement section.

3

PERFMODE

Performance Mode. Selects DAC to headphone playback performance mode.

0 = High performance playback mode.

1 = Low power playback mode.

2

HPPLYBCK

Headphone Only Playback Mode. Configures System Bias Control register bits for low

power playback when using DAC to headphone playback path only. When enabled, this

bit overrides the System Bias Control register settings. When disabled, the System Bias

Control register is used to enable system bias blocks. Set both HPPLYBCK and PER-

FMODE for lowest power consumption when using DAC to headphone playback path

only.

0 = Disabled

1 = Enabled

1

PWRSV8K

8kHz Power Save Mode. PWRSV8K configures the ADC for reduced power consump-

tion when f

S

= 8kHz. PWRSV8K can be used in conjunction with PWRSV when f

S

= 8kHz

for more power savings.

0 = Normal, high-performance mode.

1 = Low power mode.

0

PWRSV

Power Save Mode. PWRSV configures the ADC for reduced power consumption for all

sample rates. PWRSV can be used in conjunction with PWRSV8K for more power sav-

ings.

0 = Normal, high-performance mode.

1 = Low-power mode.

0x4C

7

INAEN

Line Input A Enable

0 = Disabled

1 = Enabled

6

INBEN

Line Input B Enable

0 = Disabled

1 = Enabled

3

MBEN

Microphone Bias Enable

0 = Disabled

1 = Enabled

1

ADLEN

Left ADC Enable

0 = Disabled

1 = Enabled

0

ADREN

Right ADC Enable

0 = Disabled

1 = Enabled