I2c slave address, Registers, Table 1. register map – Rainbow Electronics MAX98089 User Manual

Page 61: C slave address

���������������������������������������������������������������� Maxim Integrated Products 61

MAX98089

Low-Power, Stereo Audio Codec

with FlexSound Technology

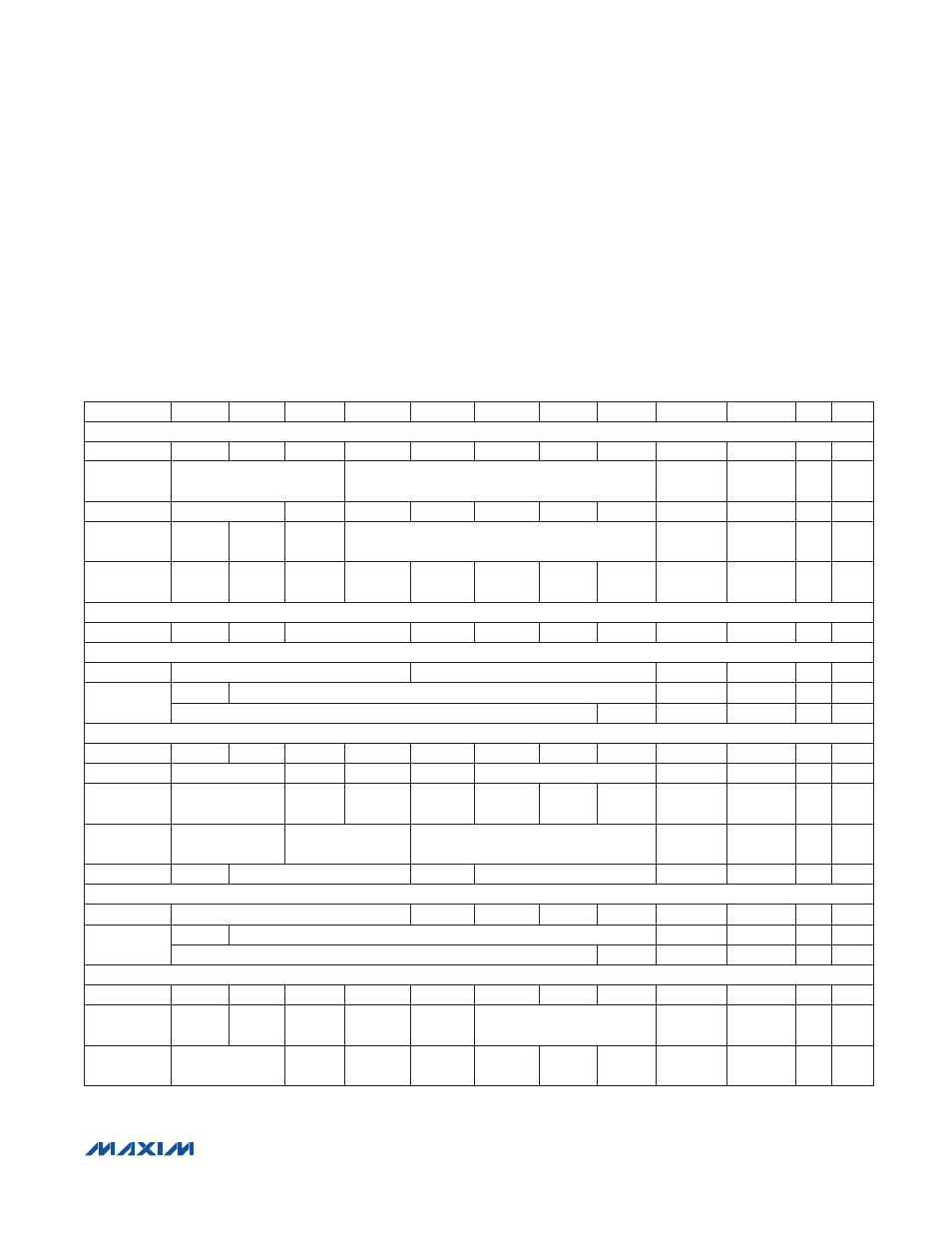

Table 1. Register Map

I

2

C Slave Address

Configure the MAX98089 using the I

2

C control bus. The

IC uses a slave address of 0x20 or 00100000 for write

operations and 0x21 or 00100001 for read operations.

See the I

2

C Serial Interface section for a complete inter-

face description.

Registers

Table 1 lists all of the registers, their addresses, and

power-on-reset states. Registers 0x00 to 0x03 and 0xFF

are read-only while all of the other registers are read/

write. Write zeros to all unused bits in the register table

when updating the register, unless otherwise noted.

REGISTER

B7

B6

B5

B4

B3

B2

B1

B0

ADDRESS DEFAULT R/W PAGE

STATUS

Status

CLD

SLD

ULK

—

—

—

JDET

—

0x00

—

R

Microphone

AGC/NG

NG

AGC

0x01

—

R

Jack Status

JKSNS

—

—

—

—

—

—

0x02

—

R

Battery

Voltage

—

—

—

VBAT

0x03

—

R/W

Interrupt

Enable

ICLD

ISLD

IULK

0

0

0

IJDET

0

0x0F

0x00

R/W

MASTER CLOCK CONTROL

Master Clock

0

0

PSCLK

0

0

0

0

0x10

0x00

R/W

DAI1 CLOCK CONTROL

Clock Mode

SR1

FREQ1

0x11

0x00

R/W 85, 86

Any Clock

Control

PLL1

NI1[14:8]

0x12

0x00

R/W

NI1[7:1]

NI1[0]

0x13

0x00

R/W

DAI1 CONFIGURATION

Format

MAS1

WCI1

BCI1

DLY1

0

TDM1

FSW1

WS1

0x14

0x00

R/W

Clock

ADC_OSR1

DAC_ORS1

0

0

BSEL1

0x15

0x00

R/W

I/O

Configuration

SEL1

LTEN1

LBEN1 DMONO1 HIZOFF1 SDOEN1 SDIEN1

0x16

0x00

R/W 81, 82

Time-Division

Multiplex

SLOTL1

SLOTR1

SLOTDLY1

0x17

0x00

R/W

Filters

MODE1

AVFLT1

DHF1

DVFLT1

0x18

0x00

R/W

DAI2 CLOCK CONTROL

Clock Mode

SR2

0

0

0

0

0x19

0x00

R/W

Any Clock

Control

PLL2

NI2[14:8]

0x1A

0x00

R/W

NI2[7:1]

NI2[0]

0x1B

0x00

R/W

DAI2 CONFIGURATION

Format

MAS2

WCI2

BCI2

DLY2

0

TDM2

FSW2

WS2

0x1C

0x00

R/W

Clock

0

0

DAC_

ORS2

0

0

BSEL2

0x1D

0x00

R/W

I/O

Configuration

SEL2

0

LBEN2 DMONO2 HIZOFF2 SDOEN2 SDIEN2

0x1E

0x00

R/W 81, 82