Tms320 second generation digital signal processors, Functional block diagram (tms320c2x) – Texas Instruments TMS320 User Manual

Page 6

TMS320 SECOND GENERATION

DIGITAL SIGNAL PROCESSORS

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

POST OFFICE BOX 1443

HOUSTON, TEXAS 77001

6

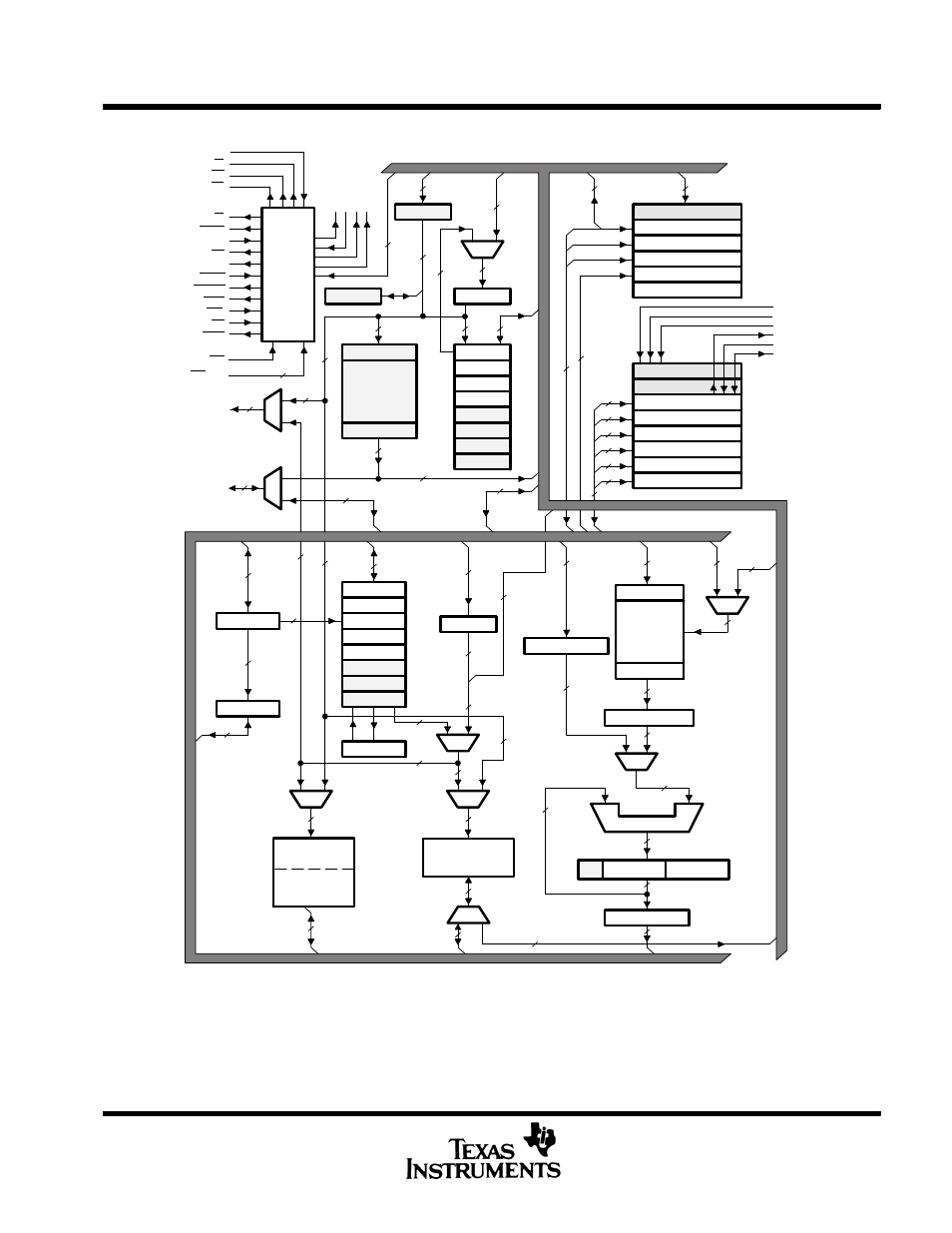

functional block diagram (TMS320C2x)

Data Bus

Data Bus

16

16

16

16

16

16

Shifters (0-7)

†

ACCL(16)

32

ACCH(16)

32

32

ALU(32)

32

32

32

Shifter(-6, 0, 1, 4)

16

Shifter(0-16)

7 LSB

From IR

9

9

16

16

16

32

TR(16)

16

Multiplier

PR(32)

DATA/PROG

RAM (256

16)

Block B0

16

16

16

16

16

Data RAM

Block B1

(256

16)

Block B2

(32

16)

3

ARB(3)

3

3

3

ARP(3)

ARAU(16)

AR4(16)

AR3(16)

AR2(16)

AR1(16)

16

AR0(16)

DP(9)

16

FSX

CLKX

DX

FSR

CLKR

DRR(16)

DXR(16)

PRD(16)

TIM(16)

IMR(6)

GREG(8)

16

16

IFR(6)

RPTC(8)

STO(16)

ST1(16)

IR(16)

3

16

16

16

16

16

D15-D0

16

16

16

16

A15-A0

INT(2-0)

MP/MC

Instruction

(8 x 16)

16

16

16

16

16

16

16

16

16

Stack

PC(16)

16

IACK

RS

BIO

MSC

HOLDA

HOLD

XF

BR

STRB

R/W

Program Bus

Program Bus

Program

ROM/

EPROM

(4096

16)

QIR(16)

16

16

16

6

8

16

16

16

X1 X2/CLKIN CL

K

O

UT1

CL

K

O

UT2

Co

nt

ro

lle

r

16

PFC(16)

MCS(16)

PS

DS

IS

SYNC

MUX

MUX

MUX

MUX

MUX

MUX

MUX

DR

MUX

MUX

C

READY

Address

AR5(16)

AR6(16)

AR7(16)

RSR(16)

XSR(16)

LEGEND:

ACCH =

Accumulator high

IFR

= Interrupt flag register

PC

= Program counter

ACCL

=

Accumulator low

IMR

= Interrupt mask register

PFC

= Prefetch counter

ALU

=

Arithmetic logic unit

IR

= Instruction register

RPTC

= Repeat instruction counter

ARAU =

Auxiliary register arithmetic unitMCS

=

Microcall stack

GREG =

Global memory allocation register

ARB

=

Auxiliary register pointer buffer

QIR

= Queue instruction register

RSR

= Serial port receive shift register

ARP

=

Auxiliary register pointer

PR

= Product register

XSR

= Serial port transmit shift register

DP

=

Data memory page pointer

PRD

= Period register for timer

AR0-AR7

= Auxiliary registers

DRR

=

Serial port data receive registerTIM

=

Timer

ST0, ST1

= Status registers

DXR

=

Serial port data transmit register

TR

= Temporary register

C

= Carry bit