Tms320 second generation digital signal processors – Texas Instruments TMS320 User Manual

Page 14

NO.

WORDS

DESCRIPTION

INSTRUCTION BIT CODE

MNEMONIC

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

PM

K

TMS320 SECOND GENERATION

DIGITAL SIGNAL PROCESSORS

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

POST OFFICE BOX 1443

HOUSTON, TEXAS 77001

14

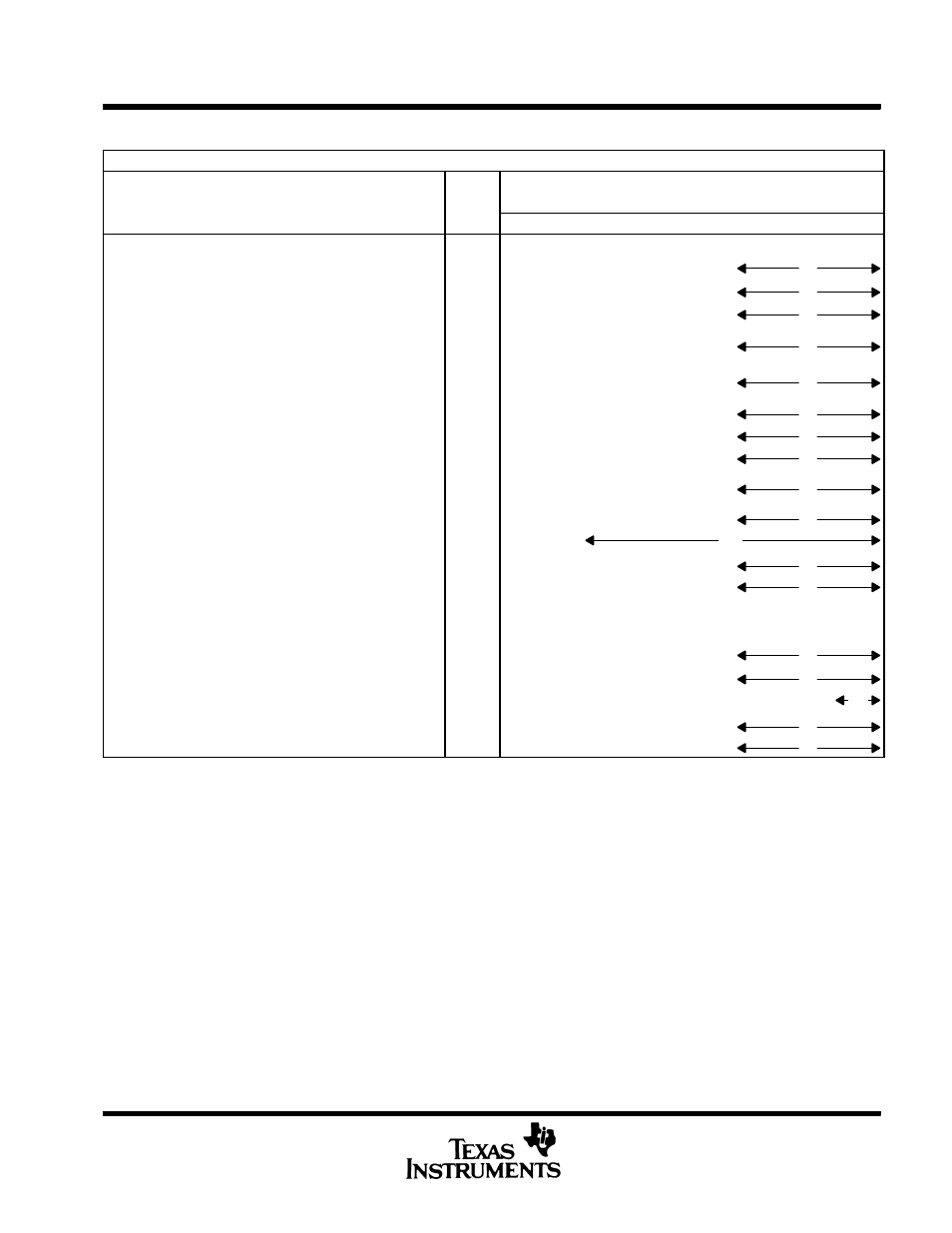

Table 3. TMS320C25 Instruction Set Summary (continued)

T REGISTER, P REGISTER, AND MULTIPLY INSTRUCTIONS

15 14 13 12 11 10 9

8 7

6 5

4 3

2 1

0

APAC

Add P register to accumulator

1

1

1

0

0

1

1

1

0 0

0 0

1 0

1 0

1

LPH

†

Load high P register

1

0

1

0

1

0

0

1

1

I

LT

Load T register

1

0

0

1

1

1

1

0

0

I

LTA

Load T register and accumulate previous product

1

0

0

1

1

1

1

0

1

I

LTD

Load T register, accumulate previous product,

and move data

1

0

0

1

1

1

1

1

1

I

LTP

†

Load T register and store P register in

accumulator

1

0

0

1

1

1

1

1

0

I

LTS

†

Load T register and subtract previous product

1

0

1

0

1

1

0

1

1

I

MAC

†

Multiply and accumulate

2

0

1

0

1

1

1

0

1

I

MACD

†

Multiply and accumulate with data move

2

0

1

0

1

1

1

0

0

I

MPY

Multiply (with T register, store product in

P register)

1

0

0

1

1

1

0

0

0

I

MPYA

‡

Multiply and accumulate previous product

1

0

0

1

1

1

0

1

0

I

MPYK

Multiply immediate

1

1

0

1

MPYS‡

Multiply and subtract previous product

1

0

0

1

1

1

0

1

1

I

MPYU‡

Multiply unsigned

1

1

1

0

0

1

1

1

1

I

PAC

Load accumulator with P register

1

1

1

0

0

1

1

1

0 0

0 0

1 0

1 0

0

SPAC

Subtract P register from accumulator

1

1

1

0

0

1

1

1

0 0

0 0

1 0

1 1

0

SPH

‡

Store high P register

1

0

1

1

1

1

1

0

1

I

SPL

‡

Store low P register

1

0

1

1

1

1

1

0

0

I

SPM

†

Set P register output shift mode

1

1

1

0

0

1

1

1

0 0

0 0

0 1

0

SQRA

†

Square and accumulate

1

0

0

1

1

1

0

0

1

I

SQRS

†

Square and subtract previous product

1

0

1

0

1

1

0

1

0

I

†

These instructions are not included in the TMS320C1x instruction set.

‡

These instructions are not included in the TMS32020 instruction set.